Page 74 -

P. 74

2.4 / EMBEDDED SYSTEMS AND THE ARM 49

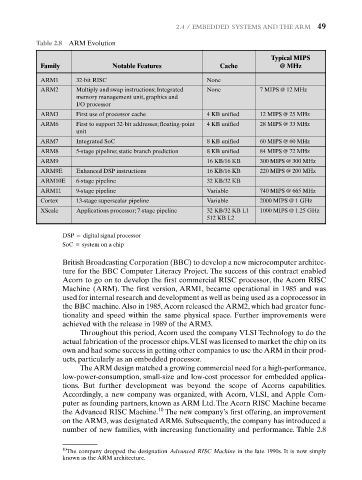

Table 2.8 ARM Evolution

Typical MIPS

Family Notable Features Cache @ MHz

ARM1 32-bit RISC None

ARM2 Multiply and swap instructions; Integrated None 7 MIPS @ 12 MHz

memory management unit, graphics and

I/O processor

ARM3 First use of processor cache 4 KB unified 12 MIPS @ 25 MHz

ARM6 First to support 32-bit addresses; floating-point 4 KB unified 28 MIPS @ 33 MHz

unit

ARM7 Integrated SoC 8 KB unified 60 MIPS @ 60 MHz

ARM8 5-stage pipeline; static branch prediction 8 KB unified 84 MIPS @ 72 MHz

ARM9 16 KB/16 KB 300 MIPS @ 300 MHz

ARM9E Enhanced DSP instructions 16 KB/16 KB 220 MIPS @ 200 MHz

ARM10E 6-stage pipeline 32 KB/32 KB

ARM11 9-stage pipeline Variable 740 MIPS @ 665 MHz

Cortex 13-stage superscalar pipeline Variable 2000 MIPS @ 1 GHz

XScale Applications processor; 7-stage pipeline 32 KB/32 KB L1 1000 MIPS @ 1.25 GHz

512 KB L2

DSP = digital signal processor

SoC = system on a chip

British Broadcasting Corporation (BBC) to develop a new microcomputer architec-

ture for the BBC Computer Literacy Project. The success of this contract enabled

Acorn to go on to develop the first commercial RISC processor, the Acorn RISC

Machine (ARM). The first version, ARM1, became operational in 1985 and was

used for internal research and development as well as being used as a coprocessor in

the BBC machine.Also in 1985,Acorn released the ARM2, which had greater func-

tionality and speed within the same physical space. Further improvements were

achieved with the release in 1989 of the ARM3.

Throughout this period, Acorn used the company VLSI Technology to do the

actual fabrication of the processor chips.VLSI was licensed to market the chip on its

own and had some success in getting other companies to use the ARM in their prod-

ucts, particularly as an embedded processor.

The ARM design matched a growing commercial need for a high-performance,

low-power-consumption, small-size and low-cost processor for embedded applica-

tions. But further development was beyond the scope of Acorns capabilities.

Accordingly, a new company was organized, with Acorn, VLSI, and Apple Com-

puter as founding partners, known as ARM Ltd. The Acorn RISC Machine became

10

the Advanced RISC Machine. The new company’s first offering, an improvement

on the ARM3, was designated ARM6. Subsequently, the company has introduced a

number of new families, with increasing functionality and performance. Table 2.8

10 The company dropped the designation Advanced RISC Machine in the late 1990s. It is now simply

known as the ARM architecture.