Page 304 - Hardware Implementation of Finite-Field Arithmetic

P. 304

284 Cha pte r Ni ne

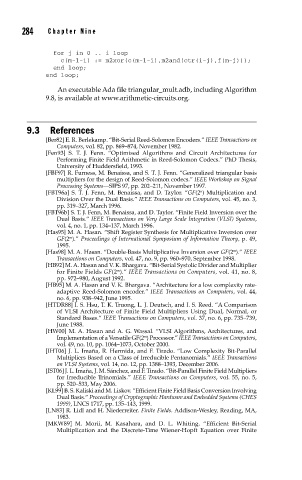

for j in 0 .. i loop

c(m-1-i) := m2xor(c(m-1-i),m2and(ctr(i-j),f(m-j)));

end loop;

end loop;

An executable Ada file triangular_mult.adb, including Algorithm

9.8, is available at www.arithmetic-circuits.org.

9.3 References

[Ber82] E. R. Berlekamp. “Bit-Serial Reed-Solomon Encoders.” IEEE Transactions on

Computers, vol. 82, pp. 869–874, November 1982.

[Fen93] S. T. J. Fenn. “Optimised Algorithms and Circuit Architectures for

Performing Finite Field Arithmetic in Reed-Solomon Codecs.” PhD Thesis,

University of Huddersfield, 1993.

[FBF97] R. Furness, M. Benaissa, and S. T. J. Fenn. “Generalized triangular basis

multipliers for the design of Reed-Solomon codecs.” IEEE Workshop on Signal

Processing Systems—SIPS 97, pp. 202–211, November 1997.

[FBT96a] S. T. J. Fenn, M. Benaissa, and D. Taylor. “GF(2 ) Multiplication and

n

Division Over the Dual Basis.” IEEE Transactions on Computers, vol. 45, no. 3,

pp. 319–327, March 1996.

[FBT96b] S. T. J. Fenn, M. Benaissa, and D. Taylor. “Finite Field Inversion over the

Dual Basis.” IEEE Transactions on Very Large Scale Integration (VLSI) Systems,

vol. 4, no. 1, pp. 134–137, March 1996.

[Has95] M. A. Hasan. “Shift Register Synthesis for Multiplicative Inversion over

GF(2 ).” Proceedings of International Symposium of Information Theory, p. 49,

m

1995.

[Has98] M. A. Hasan. “Double-Basis Multiplicative Inversion over GF(2 ).” IEEE

m

Transactions on Computers, vol. 47, no. 9, pp. 960–970, September 1998.

[HB92] M. A. Hasan and V. K. Bhargava. “Bit-Serial Systolic Divider and Multiplier

m

for Finite Fields GF(2 ).” IEEE Transactions on Computers, vol. 41, no. 8,

pp. 972–980, August 1992.

[HB95] M. A. Hasan and V. K. Bhargava. “Architecture for a low complexity rate-

adaptive Reed-Solomon encoder.” IEEE Transactions on Computers, vol. 44,

no. 6, pp. 938–942, June 1995.

[HTDR88] I. S. Hsu, T. K. Truong, L. J. Deutsch, and I. S. Reed. “A Comparison

of VLSI Architecture of Finite Field Multipliers Using Dual, Normal, or

Standard Bases.” IEEE Transactions on Computers, vol. 37, no. 6, pp. 735–739,

June 1988.

[HW00] M. A. Hasan and A. G. Wassal. “VLSI Algorithms, Architectures, and

m

Implementation of a Versatile GF(2 ) Processor.” IEEE Transactions on Computers,

vol. 49, no. 10, pp. 1064–1073, October 2000.

[IHT06] J. L. Imaña, R. Hermida, and F. Tirado. “Low Complexity Bit-Parallel

Multipliers Based on a Class of Irreducible Pentanomials.” IEEE Transactions

on VLSI Systems, vol. 14, no. 12, pp. 1388–1393, December 2006.

[IST06] J. L. Imaña, J. M. Sánchez, and F. Tirado. “Bit-Parallel Finite Field Multipliers

for Irreducible Trinomials.” IEEE Transactions on Computers, vol. 55, no. 5,

pp. 520–533, May 2006.

[KL99] B. S. Kaliski and M. Liskov. “Efficient Finite Field Basis Conversion Involving

Dual Basis.” Proceedings of Cryptographic Hardware and Embedded Systems (CHES

1999), LNCS 1717, pp. 135–143, 1999.

[LN83] R. Lidl and H. Niederreiter. Finite Fields. Addison-Wesley, Reading, MA,

1983.

[MKW89] M. Morii, M. Kasahara, and D. L. Whiting. “Efficient Bit-Serial

Multiplication and the Discrete-Time Wiener-Hopft Equation over Finite