Page 441 - Programming Microcontrollers in C

P. 441

426 Chapter 8 MCORE, A RISC Machine

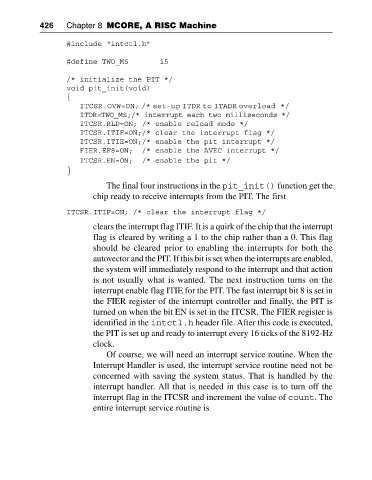

#include “intctl.h”

#define TWO_MS 15

/* initialize the PIT */

void pit_init(void)

{

ITCSR.OVW=ON; /* set-up ITDR to ITADR overload */

ITDR=TWO_MS;/* interrupt each two milliseconds */

ITCSR.RLD=ON; /* enable reload mode */

ITCSR.ITIF=ON;/* clear the interrupt flag */

ITCSR.ITIE=ON;/* enable the pit interrupt */

FIER.EF8=ON; /* enable the AVEC interrupt */

ITCSR.EN=ON; /* enable the pit */

}

The final four instructions in the pit_init() function get the

chip ready to receive interrupts from the PIT. The first

ITCSR.ITIF=ON; /* clear the interrupt flag */

clears the interrupt flag ITIF. It is a quirk of the chip that the interrupt

flag is cleared by writing a 1 to the chip rather than a 0. This flag

should be cleared prior to enabling the interrupts for both the

autovector and the PIT. If this bit is set when the interrupts are enabled,

the system will immediately respond to the interrupt and that action

is not usually what is wanted. The next instruction turns on the

interrupt enable flag ITIE for the PIT. The fast interrupt bit 8 is set in

the FIER register of the interrupt controller and finally, the PIT is

turned on when the bit EN is set in the ITCSR. The FIER register is

identified in the intctl.h header file. After this code is executed,

the PIT is set up and ready to interrupt every 16 ticks of the 8192-Hz

clock.

Of course, we will need an interrupt service routine. When the

Interrupt Handler is used, the interrupt service routine need not be

concerned with saving the system status. That is handled by the

interrupt handler. All that is needed in this case is to turn off the

interrupt flag in the ITCSR and increment the value of count. The

entire interrupt service routine is