Page 118 - ARM 64 Bit Assembly Language

P. 118

104 Chapter 4

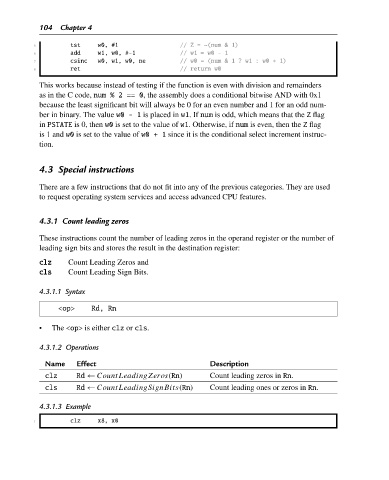

5 tst w0, #1 // Z = ~(num & 1)

6 add w1, w0, #-1 // w1 = w0 - 1

7 csinc w0, w1, w0, ne // w0 =(num&1?w1 :w0+1)

8 ret // return w0

This works because instead of testing if the function is even with division and remainders

as in the C code, num % 2 == 0, the assembly does a conditional bitwise AND with 0x1

because the least significant bit will always be 0 for an even number and 1 for an odd num-

ber in binary. The value w0 - 1 is placed in w1.If num is odd, which means that the Z flag

in PSTATE is 0, then w0 is set to the value of w1.Otherwise,if num is even, then the Z flag

is 1 and w0 is set to the value of w0+1 since it is the conditional select increment instruc-

tion.

4.3 Special instructions

There are a few instructions that do not fit into any of the previous categories. They are used

to request operating system services and access advanced CPU features.

4.3.1 Count leading zeros

These instructions count the number of leading zeros in the operand register or the number of

leading sign bits and stores the result in the destination register:

clz Count Leading Zeros and

cls Count Leading Sign Bits.

4.3.1.1 Syntax

<op> Rd, Rn

• The <op> is either clz or cls.

4.3.1.2 Operations

Name Effect Description

clz Rd ← CountLeadingZeros(Rn) Count leading zeros in Rn.

cls Rd ← CountLeadingSignBits(Rn) Count leading ones or zeros in Rn.

4.3.1.3 Example

1 clz x8, x0