Page 381 - ARM 64 Bit Assembly Language

P. 381

Advanced SIMD instructions 371

• If Ts is s,then Vm must be in the range s0 to s15.

• If x is present, then 0 ×±∞ → ±2 (vector).

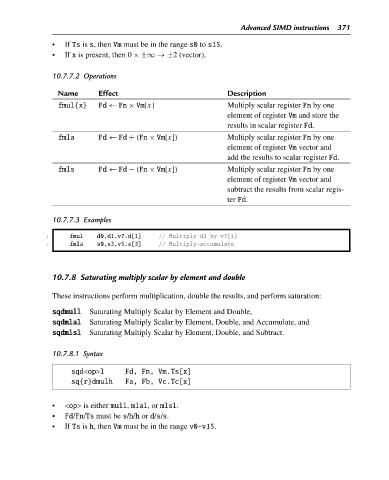

10.7.7.2 Operations

Name Effect Description

fmul{x} Fd ← Fn × Vm[x] Multiply scalar register Fn by one

element of register Vm and store the

results in scalar register Fd.

fmla Fd ← Fd + (Fn × Vm[x]) Multiply scalar register Fn by one

element of register Vm vector and

add the results to scalar register Fd.

fmls Fd ← Fd − (Fn × Vm[x]) Multiply scalar register Fn by one

element of register Vm vector and

subtract the results from scalar regis-

ter Fd.

10.7.7.3 Examples

1 fmul d0,d1,v7.d[1] // Multiply d1 by v7[i]

2 fmla s0,s3,v5.s[3] // Multiply-accumulate

10.7.8 Saturating multiply scalar by element and double

These instructions perform multiplication, double the results, and perform saturation:

sqdmull Saturating Multiply Scalar by Element and Double,

sqdmlal Saturating Multiply Scalar by Element, Double, and Accumulate, and

sqdmlsl Saturating Multiply Scalar by Element, Double, and Subtract.

10.7.8.1 Syntax

sqd<op>l Fd, Fn, Vm.Ts[x]

sq{r}dmulh Fa, Fb, Vc.Tc[x]

• <op> is either mull, mlal,or mlsl.

• Fd/Fn/Ts must be s/h/h or d/s/s.

• If Ts is h,then Vm must be in the range v0-v15.