Page 558 - Introduction to Information Optics

P. 558

9.5. Conversion between Different Number Systems 543

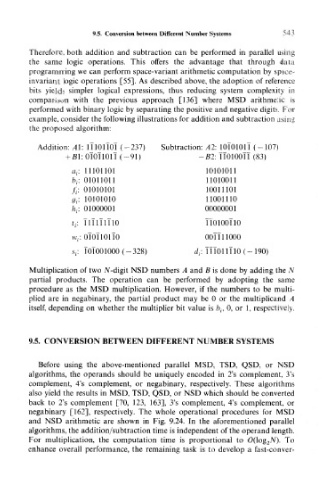

Therefore, both addition and subtraction can be performed in parallel using

the same logic operations. This offers the advantage that through data

programming we can perform space-variant arithmetic computation by space-

invariant logic operations [55]. As described above, the adoption of reference

bits yields simpler logical expressions, thus reducing system complexity in

comparison with the previous approach [136] where MSD arithmetic is

performed with binary logic by separating the positive and negative digits. For

example, consider the following illustrations for addition and subtraction using

the proposed algorithm:

Addition; A\: 11101101 (-237) Subtraction: A2: JjOlOlOH (- 107)

+ 51:01011011 (-91) -B2: IlOlOOTI (83)

a t: 11101101 10101011

bfi 01011011 11010011

/;.: 01010101 10011101

g{. 10101010 11001110

\: 01000001 00000001

t {\ III 111 110 Iloioolio

w,.: OlOllOllO OOllllOOO

s,-: M001000(-328) - IIT011110(

Multiplication of two N-digit NSD numbers A and B is done by adding the N

partial products. The operation can be performed by adopting the same

procedure as the MSD multiplication. However, if the numbers to be multi-

plied are in negabinary, the partial product may be 0 or the multiplicand A

itself, depending on whether the multiplier bit value is b {, 0, or 1, respectively.

9.5. CONVERSION BETWEEN DIFFERENT NUMBER SYSTEMS

Before using the above-mentioned parallel MSD, TSD, QSD, or NSD

algorithms, the operands should be uniquely encoded in 2's complement, 3's

complement, 4's complement, or negabinary, respectively. These algorithms

also yield the results in MSD, TSD, QSD, or NSD which should be converted

back to 2's complement [70, 123, 163], 3's complement, 4's complement, or

negabinary [162], respectively. The whole operational procedures for MSD

and NSD arithmetic are shown in Fig. 9.24. In the aforementioned parallel

algorithms, the addition/subtraction time is independent of the operand length.

For multiplication, the computation time is proportional to 0(log 2,/V). To

enhance overall performance, the remaining task is to develop a fast-conver-