Page 222 - Introduction to Microcontrollers Architecture, Programming, and Interfacing of The Motorola 68HC12

P. 222

7.4 Long Integer Arithmetic 199

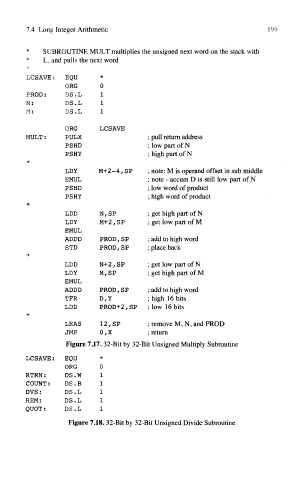

* SUBROUTINE MULT multiplies the unsigned next word on the stack with

* L, and pulls the next word

sK

LCSAVE: EQU *

ORG 0

PROD: DS.L 1

N: DS.L 1

M: DS.L 1

ORG LCSAVE

MULT: PULX ; pull return address

PSHD ; low part of N

PSHY ; high part of N

*

LDY M+2 - 4, SP ; note: M is operand offset in sub middle

EMUL ; note - accum D is still low part of N

PSHD ; low word of product

PSHY ; high word of product

*

LDD N, SP ; get high part of N

LDY M+2, SP ; get low part of M

EMUL

ADDD PROD, SP ; add to high word

STD PROD r SP ; place back

*

LDD N+2, SP ; get low part of N

LDY M, SP ; get high part of M

EMUL

ADDD PROD, SP ; add to high word

TFR D,Y ; high 16 bits

LDD PROD+2 , SP ; low 16 bits

*

LEAS 12, SP ; remove M, N, and PROD

JMP 0, X ; return

Figure 7.17.32-Bit by 32-Bit Unsigned Multiply Subroutine

LCSAVE: EQU *

ORG 0

RTRN: DS.W 1

COUNT: DS.B 1

DVS: DS.L 1

REM: DS.L 1

QUOT: DS.L 1

Figure 7.18. 32-Bit by 32-Bit Unsigned Divide Subroutine