Page 227 - Making PIC Microcontroller Instruments and Controllers

P. 227

224 CREATI G ACCURATE II{TENVATS WITH TI EN+ THE METRONOiIES

Note mis ptugram will be nodified for each of the timers, but since it does not reallv

change when the other tiners are usetl, I rNill not list this progrcm again The changes

to the tiners wiU be the sdrne as will be ade for the LCD on the LAB Xl. These

changes are listed under each timer section.

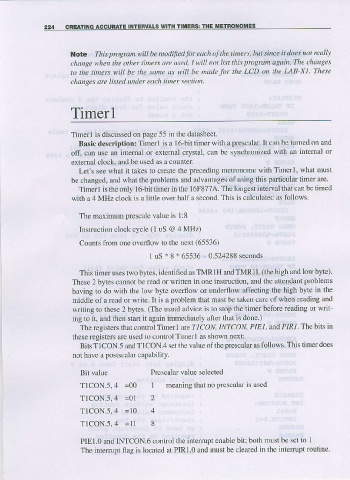

Timerl

Timerl is discussed on page 55 in the datasheet.

Basic description: Timerl is a 16-bit timer with a prcscalar. It can be turned on and

off, can use an internal or extemal crystal, can be syncbrcnized wjth an intemal or

external clock, and be used as a counter.

Let's see what it takes to create the preceding metronome with Timl3rl, what must

be changed, and what the problems and advantages of using thjs particular timer are

Tjmerl is the only I 6-bit timer in the 16F877A. The longest interval that can be timed

with a4 MHz clock is a little over half a second. This is calculated as follows.

The maximumprescale value is 1:8

Instruction clock cycle (1 uS @ 4 MHz)

Counts from one overflow to the next (65536)

* +

I uS 8 65536=0.52288 seconds

This timeruses two bytes, identified as TMRIH and TMRI L (the high and Iow byte).

These 2 bytes cannot be read or wdtten in one instruction, and the attendant Foblems

having to do with the low byte overflow or underflow affecting tho high byte in the

middle of a read or write. It is a problem that must be taken care of when rcading and

writing to these 2 bytes. (The usual advice is to stop the tlmer beforc reading or writ_

ing to it, and then start it again immediately after that is done.)

The registers that control Timerl are ZCON, .I.\TCO,V, Pltl, and PIRJ The bits in

these registers are used to controlTimerl as shown next:

as follows This timerdoes

Bits Tl CON.5 aIId T1CON.4 set the value ofthe Fescalar

not have a postscalar capability.

Bit value Prescalar value selected

TlCON.5,4 =00 1 meaning thal no prescalar is used

TlCON.5,4 =01 2

T1CON.5,4 =10

=

T1CON.5,4 ll 8

PIE1.0 and INTCON.6 controi the interrupt enable biti both must be set to I

The interrupt flag is located at PIRI .0 and must be cleared in the intenupt rortine.