Page 156 - The Art of Designing Embedded Systems

P. 156

Troubleshooting Tools 143

I data bus

clock

serial-in

serial-out

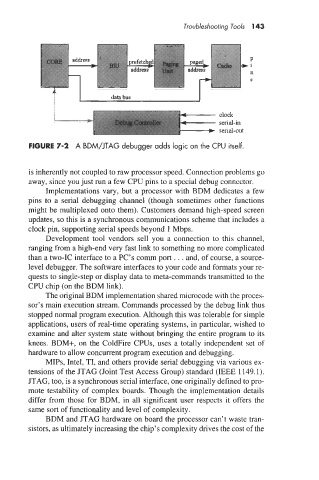

FIGURE 7-2 A BDM/JTAG debugger adds logic on the CPU itself.

is inherently not coupled to raw processor speed. Connection problems go

away, since you just run a few CPU pins to a special debug connector.

Implementations vary, but a processor with BDM dedicates a few

pins to a serial debugging channel (though sometimes other functions

might be multiplexed onto them). Customers demand high-speed screen

updates, so this is a synchronous communications scheme that includes a

clock pin, supporting serial speeds beyond 1 Mbps.

Development tool vendors sell you a connection to this channel,

ranging from a high-end very fast link to something no more complicated

than a two-IC interface to a PC’s comm port . . . and, of course, a source-

level debugger. The software interfaces to your code and formats your re-

quests to single-step or display data to meta-commands transmitted to the

CPU chip (on the BDM link).

The original BDM implementation shared microcode with the proces-

sor’s main execution stream. Commands processed by the debug link thus

stopped normal program execution. Although this was tolerable for simple

applications, users of real-time operating systems, in particular, wished to

examine and alter system state without bringing the entire program to its

knees. BDM+, on the ColdFire CPUs, uses a totally independent set of

hardware to allow concurrent program execution and debugging.

MIPS, Intel, TI, and others provide serial debugging via various ex-

tensions of the JTAG (Joint Test Access Group) standard (IEEE 1149.1).

JTAG, too, is a synchronous serial interface, one originally defined to pro-

mote testability of complex boards. Though the implementation details

differ from those for BDM, in all significant user respects it offers the

same sort of functionality and level of complexity.

BDM and JTAG hardware on board the processor can’t waste tran-

sistors, as ultimately increasing the chip’s complexity drives the cost of the