Page 375 - Analog and Digital Filter Design

P. 375

372 Analog and Digital Filter Design

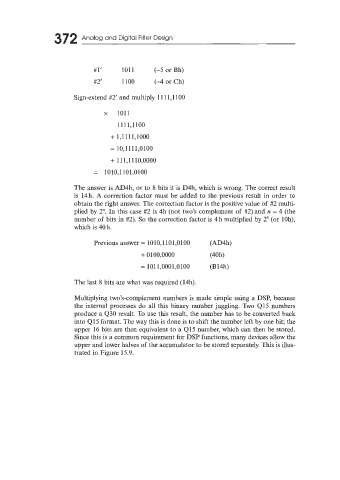

#1’ 101 1 (-5 or Bh)

#2’ 1100 (-4 or Ch)

Sign-extend #2’ and multiply 1 1 1 1,1100

x 1011

1 1 1 1,1100

+ 1,1111,1000

= 10,1111,0100

+ 111,1110,0000

= 1010,1101,0100

The answer is AD4h, or to 8 bits it is D4h, which is wrong. The correct result

is 14h. A correction factor must be added to the previous result in order to

obtain the right answer. The correction factor is the positive value of #2 multi-

plied by 2”. In this case #2 is 4h (not two’s complement of #2) and n = 4 (the

number of bits in #2). So the correction factor is 4h multiplied by 2‘ (or lOh),

which is 40 h.

Previous answer = 1010,1101,0100 (AD4h)

+ 0100,0000 (40h)

= 101 1,0001,0100 (B14h)

The last 8 bits are what was required (14h).

Multiplying two’s-complement numbers is made simple using a DSP, because

the internal processes do all this binary number juggling. Two Q15 numbers

produce a 430 result. To use this result, the number has to be converted back

into Q15 format. The way this is done is to shift the number left by one bit; the

upper 16 bits are then equivalent to a Q15 number, which can then be stored.

Since this is a common requirement for DSP functions, many devices allow the

upper and lower halves of the accumulator to be stored separately. This is illus-

trated in Figure 15.9.