Page 185 - Bebop to The Boolean Boogie An Unconventional Guide to Electronics Fundamentals, Components, and Processes

P. 185

166 Chapter Fifteen

This operation, known as refreshing, requires the contents of each cell to be read

out and then rewritten. Some types of DRAM require external circuitry to

supervise the refresh process, in which case a special independent controller

device is employed to manage a group of DRAMS. In other cases, a DRAM

may contain its own internal self-refresh circuitry.

In the case of Static RAMS (SRAMs) ,7 each cell is formed from four or six

transistors configured as a latch or a flip-flop. The term “static” is applied

because, once a value has been loaded into an SRAM cell, it will remain

unchanged until it is explicitly altered or until power is removed from

the device.

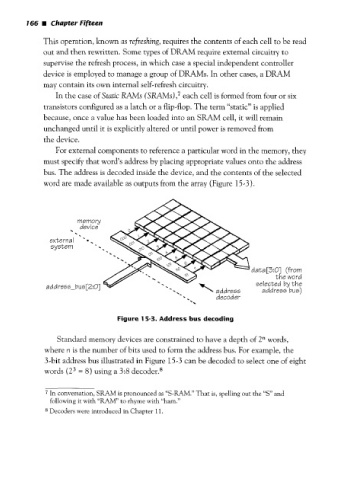

For external components to reference a particular word in the memory, they

must specify that word’s address by placing appropriate values onto the address

bus. The address is decoded inside the device, and the contents of the selected

word are made available as outputs from the array (Figure 15-3).

memory

.

device

.

external ‘ .

system

data[3:0] (from

the word

address_bus[2:O] selected by the

. decoder

address bus)

Figure 15-3. Address bus decoding

Standard memory devices are constrained to have a depth of 2” words,

where n is the number of bits used to form the address bus. For example, the

3-bit address bus illustrated in Figure 15-3 can be decoded to select one of eight

words ( z3 = 8) using a 3:8 decoder.8

7 In conversation, SRAM is pronounced as “S-RAM.” That is, spelling out the “S” and

following it with “RAM” to rhyme with “ham.”

8 Decoders were introduced in Chapter 11.