Page 191 - Bebop to The Boolean Boogie An Unconventional Guide to Electronics Fundamentals, Components, and Processes

P. 191

7 72 Chapter Fifteen

read -write

address-bus[lO:O]

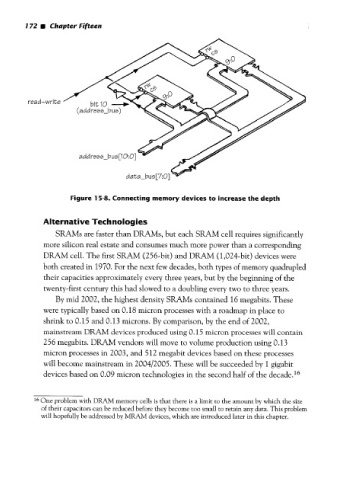

Figure 15-8. Connecting memory devices to increase the depth

AI ternat ive Tech nolog ies

SRAMs are faster than DRAMS, but each SRAM cell requires significantly

more silicon real estate and consumes much more power than a corresponding

DRAM cell. The first SRAM (256-bit) and DRAM (1,024-bit) devices were

both created in 1970. For the next few decades, both types of memory quadrupled

their capacities approximately every three years, but by the beginning of the

twenty-first century this had slowed to a doubling every two to three years.

By mid 2002, the highest density SRAMs contained 16 megabits. These

were typically based on 0.18 micron processes with a roadmap in place to

shrink to 0.15 and 0.13 microns. By comparison, by the end of 2002,

mainstream DRAM devices produced using 0.15 micron processes will contain

256 megabits. DRAM vendors will move to volume production using 0.13

micron processes in 2003, and 5 12 megabit devices based on these processes

will become mainstream in 2004/2005. These will be succeeded by 1 gigabit

devices based on 0.09 micron technologies in the second half of the decade.16

16 One problem with DRAM memory cells is that there is a limit to the amount by which the size

of their capacitors can be reduced before they become too small to retain any data. This problem

will hopefully be addressed by MRAM devices, which are introduced later in this chapter.