Page 52 -

P. 52

28 CHAPTER 2 / COMPUTER EVOLUTION AND PERFORMANCE

Mag tape

units

CPU

Card

punch

Data

channel

Line

printer

Card

reader

Drum

Multi Data

plexor channel

Disk

Data

Disk

channel

Hyper

tapes

Memory

Data Teleprocessing

channel equipment

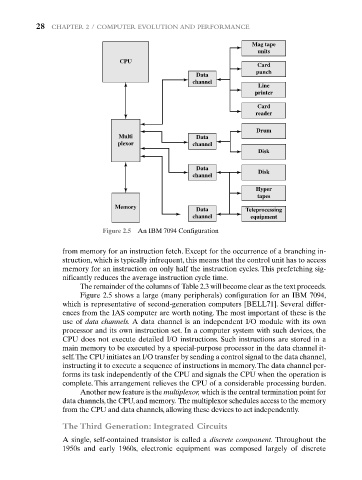

Figure 2.5 An IBM 7094 Configuration

from memory for an instruction fetch. Except for the occurrence of a branching in-

struction, which is typically infrequent, this means that the control unit has to access

memory for an instruction on only half the instruction cycles. This prefetching sig-

nificantly reduces the average instruction cycle time.

The remainder of the columns of Table 2.3 will become clear as the text proceeds.

Figure 2.5 shows a large (many peripherals) configuration for an IBM 7094,

which is representative of second-generation computers [BELL71]. Several differ-

ences from the IAS computer are worth noting. The most important of these is the

use of data channels. A data channel is an independent I/O module with its own

processor and its own instruction set. In a computer system with such devices, the

CPU does not execute detailed I/O instructions. Such instructions are stored in a

main memory to be executed by a special-purpose processor in the data channel it-

self.The CPU initiates an I/O transfer by sending a control signal to the data channel,

instructing it to execute a sequence of instructions in memory.The data channel per-

forms its task independently of the CPU and signals the CPU when the operation is

complete. This arrangement relieves the CPU of a considerable processing burden.

Another new feature is the multiplexor, which is the central termination point for

data channels,the CPU,and memory. The multiplexor schedules access to the memory

from the CPU and data channels, allowing these devices to act independently.

The Third Generation: Integrated Circuits

A single, self-contained transistor is called a discrete component. Throughout the

1950s and early 1960s, electronic equipment was composed largely of discrete