Page 234 - DSP Integrated Circuits

P. 234

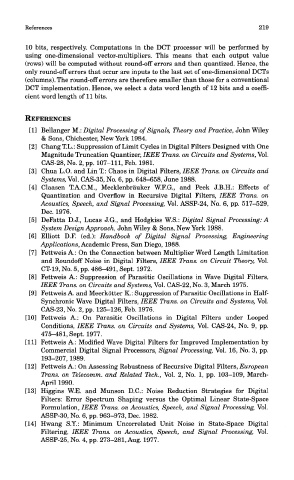

References 219

10 bits, respectively. Computations in the DCT processor will be performed by

using one-dimensional vector-multipliers. This means that each output value

(rows) will be computed without round-off errors and then quantized. Hence, the

only round-off errors that occur are inputs to the last set of one-dimensional DCTs

(columns). The round-off errors are therefore smaller than those for a conventional

DCT implementation. Hence, we select a data word length of 12 bits and a coeffi-

cient word length of 11 bits.

REFERENCES

[1] Bellanger M.: Digital Processing of Signals, Theory and Practice, John Wiley

& Sons, Chichester, New York 1984.

[2] Chang T.L.: Suppression of Limit Cycles in Digital Filters Designed with One

Magnitude Truncation Quantizer, IEEE Trans, on Circuits and Systems, Vol.

CAS-28, No. 2, pp. 107-111, Feb. 1981.

[3] Chua L.O. and Lin T: Chaos in Digital Filters, IEEE Trans, on Circuits and

Systems, Vol. CAS-35, No. 6, pp. 648-658, June 1988.

[4] Claasen T.A.C.M., Mecklenbrauker W.F.G., and Peek J.B.H.: Effects of

Quantization and Overflow in Recursive Digital Filters, IEEE Trans, on

Acoustics, Speech, and Signal Processing, Vol. ASSP-24, No. 6, pp. 517—529,

Dec. 1976.

[5] DeFatta D.J., Lucas J.G., and Hodgkiss W.S.: Digital Signal Processing: A

System Design Approach, John Wiley & Sons, New York 1988.

[6] Elliott D.F. (ed.): Handbook of Digital Signal Processing, Engineering

Applications, Academic Press, San Diego, 1988.

[7] Fettweis A.: On the Connection between Multiplier Word Length Limitation

and Roundoff Noise in Digital Filters, IEEE Trans, on Circuit Theory, Vol.

CT-19, No. 5, pp. 486-491, Sept. 1972.

[8] Fettweis A.: Suppression of Parasitic Oscillations in Wave Digital Filters,

IEEE Trans, on Circuits and Systems, Vol. CAS-22, No. 3, March 1975.

[9] Fettweis A. and Meerkotter K.: Suppression of Parasitic Oscillations in Half-

Synchronic Wave Digital Filters, IEEE Trans, on Circuits and Systems, Vol.

CAS-23, No. 2, pp. 125-126, Feb. 1976.

[10] Fettweis A.: On Parasitic Oscillations in Digital Filters under Looped

Conditions, IEEE Trans, on Circuits and Systems, Vol. CAS-24, No. 9, pp.

475-481, Sept. 1977.

[11] Fettweis A.: Modified Wave Digital Filters for Improved Implementation by

Commercial Digital Signal Processors, Signal Processing, Vol. 16, No. 3, pp.

193-207, 1989.

[12] Fettweis A.: On Assessing Robustness of Recursive Digital Filters, European

Trans, on Telecomm. and Related Tech., Vol. 2, No. 1, pp. 103-109, March-

April 1990.

[13] Higgins WE. and Munson D.C.: Noise Reduction Strategies for Digital

Filters: Error Spectrum Shaping versus the Optimal Linear State-Space

Formulation, IEEE Trans, on Acoustics, Speech, and Signal Processing, Vol.

ASSP-30, No. 6, pp. 963-973, Dec. 1982.

[14] Hwang S.Y.: Minimum Uncorrelated Unit Noise in State-Space Digital

Filtering, IEEE Trans, on Acoustics, Speech, and Signal Processing, Vol.

ASSP-25, No. 4, pp. 273-281, Aug. 1977.