Page 195 - Engineering Digital Design

P. 195

166 CHAPTER 4 / LOGIC FUNCTION REPRESENTATION AND MINIMIZATION

l~ CDE (A+D+E) -^

\

\ CD / C \ CD C

AB\ 00 °V 11 10 I AB\. 00 11 ^ (B+D)

V

,-r \ °\ -|/

h

00 E' 00 NO; E^ 0 (£/J

0 1 3 2 0 1 3 2

-i^— BCDE

/*"=•>* X J _ x (C+E)

01 E E 01,^ u E 0 b

^ /

4 5 7 6 B (A+C+D) — "^ 4 5 7 ^ 6

11 [C.i 1] E E 1 11 1 1 E E

r 12 15 ~L_j 14- r \ 12 13 15 14

A r ^ A

/ ^- ABE

10 / fc 10 >'o) fp 0 70\!

/ 8 9 11 10/ / 8 / 9 11 \ioV

/ i . ^SOP

- / D / D

ABC-' (B+EH

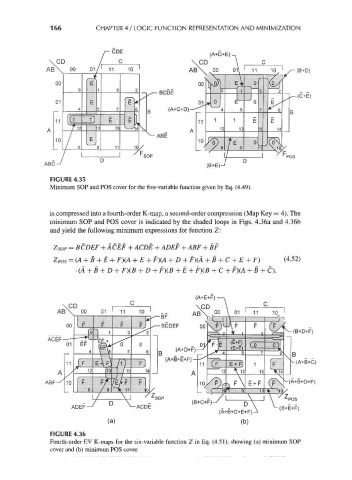

FIGURE 4.35

Minimum SOP and POS cover for the five-variable function given by Eq. (4.49).

is compressed into a fourth-order K-map, a second-order compression (Map Key = 4). The

minimum SOP and POS cover is indicated by the shaded loops in Figs. 4.36a and 4.36b

and yield the following minimum expressions for function Z:

ZSQP = B CDEF + A CEF + ACDE + ADEF + ABF + BF

(A+B+E+F)(A + E+F)(A + D + F)(A+B + C + E + F) (4.52)

• (A + B + D + F}(B + D + F)(B +E + F)(B + C + F}(A + B + C).

(B+D+F)

FIGURE 4.36

Fourth-order EV K-maps for the six-variable function Z in Eq. (4.51), showing (a) minimum SOP

cover and (b) minimum POS cover.