Page 103 - Hardware Implementation of Finite-Field Arithmetic

P. 103

86 Cha pte r T h ree

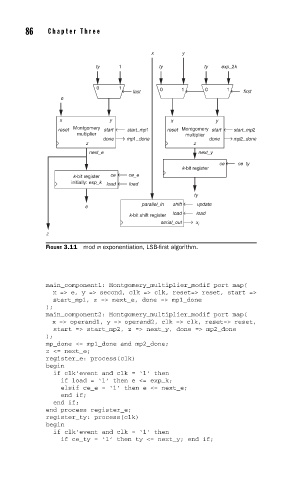

x y

ty 1 ty ty exp_2k

0 1

last 0 1 0 1 first

e

x y x y

reset Montgomery start start_mp1 reset Montgomery start start_mp2

multiplier multiplier

done mp1_done done mp2_done

z z

next_e next_y

ce ce_ty

k-bit register

k-bit register ce ce_e

initially: exp_k load load

ty

parallel_in shift update

e

load load

k-bit shift register

serial_out x

i

z

FIGURE 3.11 mod m exponentiation, LSB-fi rst algorithm.

main_component1: Montgomery_multiplier_modif port map(

x => e, y => second, clk => clk, reset=> reset, start =>

start_mp1, z => next_e, done => mp1_done

);

main_component2: Montgomery_multiplier_modif port map(

x => operand1, y => operand2, clk => clk, reset=> reset,

start => start_mp2, z => next_y, done => mp2_done

);

mp_done <= mp1_done and mp2_done;

z <= next_e;

register_e: process(clk)

begin

if clk’event and clk = ‘1’ then

if load = ‘1’ then e <= exp_k;

elsif ce_e = ‘1’ then e <= next_e;

end if;

end if;

end process register_e;

register_ty: process(clk)

begin

if clk’event and clk = ‘1’ then

if ce_ty = ‘1’ then ty <= next_y; end if;