Page 39 - Introduction to Microcontrollers Architecture, Programming, and Interfacing of The Motorola 68HC12

P. 39

16 Chapter 1 Basic Computer Structure and the 6812

the end of the chapters. We want you to optimize static efficiency in your solutions,

unless we state otherwise in the problem. Learning to work toward a goal should help

you write better programs for any application when you train yourself to try to

understand what goal you are working toward.

1.4 MC68HC812A4 and MC68HC912B32 Organizations

The 6812 is currently available in two implementations, which are designated the

MC68HC812A4 (abbreviated the 'A4) and MC68HC912B32 (abbreviated the 'B32).

These are discussed herein.

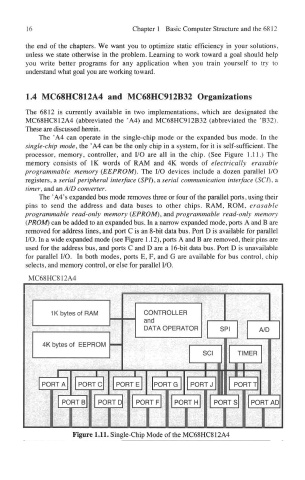

The 'A4 can operate in the single-chip mode or the expanded bus mode. In the

single-chip mode, the 'A4 can be the only chip in a system, for it is self-sufficient. The

processor, memory, controller, and I/O are all in the chip. (See Figure 1.11.) The

memory consists of IK words of RAM and 4K words of electrically erasable

programmable memory (EEPROM). The I/O devices include a dozen parallel I/O

registers, a serial peripheral interface (SPI), a serial communication interface (SCI), a

timer, and an AID converter.

The ' A4's expanded bus mode removes three or four of the parallel ports, using their

pins to send the address and data buses to other chips. RAM, ROM, erasable

programmable read-only memory (EPROM), and programmable read-only memory

(PROM) can be added to an expanded bus. In a narrow expanded mode, ports A and B are

removed for address lines, and port C is an 8-bit data bus. Port D is available for parallel

I/O. In a wide expanded mode (see Figure 1.12), ports A and B are removed, their pins are

used for the address bus, and ports C and D are a 16-bit data bus. Port D is unavailable

for parallel I/O. In both modes, ports E, F, and G are available for bus control, chip

selects, and memory control, or else for parallel I/O.

Figure 1.11. Single-Chip Mode of the MC68HC812A4