Page 349 - System on Package_ Miniaturization of the Entire System

P. 349

Integrated Chip-to-Chip Optoelectr onic SOP 323

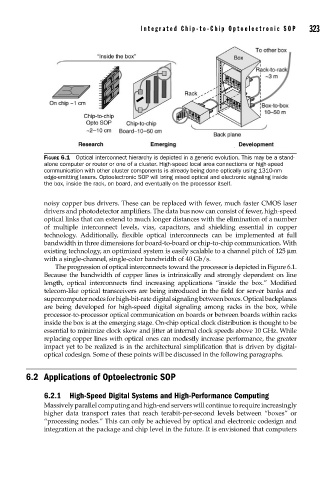

FIGURE 6.1 Optical interconnect hierarchy is depicted in a generic evolution. This may be a stand-

alone computer or router or one of a cluster. High-speed local area connections or high-speed

communication with other cluster components is already being done optically using 1310-nm

edge-emitting lasers. Optoelectronic SOP will bring mixed optical and electronic signaling inside

the box, inside the rack, on board, and eventually on the processor itself.

noisy copper bus drivers. These can be replaced with fewer, much faster CMOS laser

drivers and photodetector amplifiers. The data bus now can consist of fewer, high-speed

optical links that can extend to much longer distances with the elimination of a number

of multiple interconnect levels, vias, capacitors, and shielding essential in copper

technology. Additionally, flexible optical interconnects can be implemented at full

bandwidth in three dimensions for board-to-board or chip-to-chip communication. With

existing technology, an optimized system is easily scalable to a channel pitch of 125 μm

with a single-channel, single-color bandwidth of 40 Gb/s.

The progression of optical interconnects toward the processor is depicted in Figure 6.1.

Because the bandwidth of copper lines is intrinsically and strongly dependent on line

length, optical interconnects find increasing applications “inside the box.” Modified

telecom-like optical transceivers are being introduced in the field for server banks and

supercomputer nodes for high-bit-rate digital signaling between boxes. Optical backplanes

are being developed for high-speed digital signaling among racks in the box, while

processor-to-processor optical communication on boards or between boards within racks

inside the box is at the emerging stage. On-chip optical clock distribution is thought to be

essential to minimize clock skew and jitter at internal clock speeds above 10 GHz. While

replacing copper lines with optical ones can modestly increase performance, the greater

impact yet to be realized is in the architectural simplification that is driven by digital-

optical codesign. Some of these points will be discussed in the following paragraphs.

6.2 Applications of Optoelectronic SOP

6.2.1 High-Speed Digital Systems and High-Performance Computing

Massively parallel computing and high-end servers will continue to require increasingly

higher data transport rates that reach terabit-per-second levels between “boxes” or

“processing nodes.” This can only be achieved by optical and electronic codesign and

integration at the package and chip level in the future. It is envisioned that computers