Page 224 - A Practical Guide from Design Planning to Manufacturing

P. 224

Logic Design 197

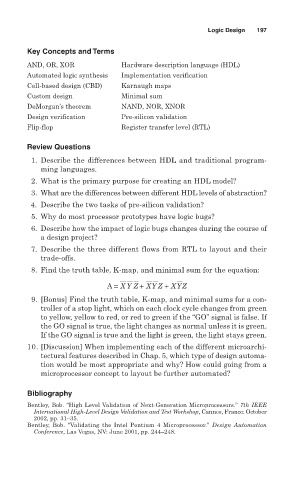

Key Concepts and Terms

AND, OR, XOR Hardware description language (HDL)

Automated logic synthesis Implementation verification

Cell-based design (CBD) Karnaugh maps

Custom design Minimal sum

DeMorgan’s theorem NAND, NOR, XNOR

Design verification Pre-silicon validation

Flip-flop Register transfer level (RTL)

Review Questions

1. Describe the differences between HDL and traditional program-

ming languages.

2. What is the primary purpose for creating an HDL model?

3. What are the differences between different HDL levels of abstraction?

4. Describe the two tasks of pre-silicon validation?

5. Why do most processor prototypes have logic bugs?

6. Describe how the impact of logic bugs changes during the course of

a design project?

7. Describe the three different flows from RTL to layout and their

trade-offs.

8. Find the truth table, K-map, and minimal sum for the equation:

___ ___ ___ ___ ___ ___

A = XY Z + XY Z + XYZ

9. [Bonus] Find the truth table, K-map, and minimal sums for a con-

troller of a stop light, which on each clock cycle changes from green

to yellow, yellow to red, or red to green if the “GO” signal is false. If

the GO signal is true, the light changes as normal unless it is green.

If the GO signal is true and the light is green, the light stays green.

10. [Discussion] When implementing each of the different microarchi-

tectural features described in Chap. 5, which type of design automa-

tion would be most appropriate and why? How could going from a

microprocessor concept to layout be further automated?

Bibliography

Bentley, Bob. “High Level Validation of Next-Generation Microprocessors.” 7th IEEE

International High-Level Design Validation and Test Workshop, Cannes, France: October

2002, pp. 31–35.

Bentley, Bob. “Validating the Intel Pentium 4 Microprocessor.” Design Automation

Conference, Las Vegas, NV: June 2001, pp. 244–248.