Page 91 - A Practical Guide from Design Planning to Manufacturing

P. 91

Computer Components 67

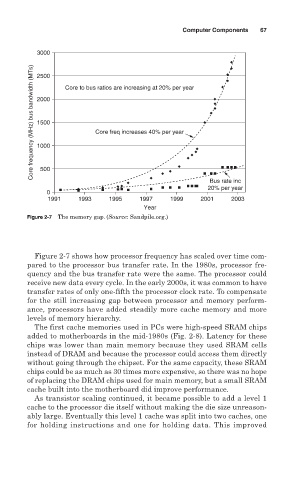

3000 Core to bus ratios are increasing at 20% per year

Core frequency (MHz) bus bandwidth (MTs) 2000 Core freq increases 40% per year

2500

1500

1000

500

Bus rate inc

20% per year

0

1991 1993 1995 1997 1999 2001 2003

Year

Figure 2-7 The memory gap. (Source: Sandpile.org.)

Figure 2-7 shows how processor frequency has scaled over time com-

pared to the processor bus transfer rate. In the 1980s, processor fre-

quency and the bus transfer rate were the same. The processor could

receive new data every cycle. In the early 2000s, it was common to have

transfer rates of only one-fifth the processor clock rate. To compensate

for the still increasing gap between processor and memory perform-

ance, processors have added steadily more cache memory and more

levels of memory hierarchy.

The first cache memories used in PCs were high-speed SRAM chips

added to motherboards in the mid-1980s (Fig. 2-8). Latency for these

chips was lower than main memory because they used SRAM cells

instead of DRAM and because the processor could access them directly

without going through the chipset. For the same capacity, these SRAM

chips could be as much as 30 times more expensive, so there was no hope

of replacing the DRAM chips used for main memory, but a small SRAM

cache built into the motherboard did improve performance.

As transistor scaling continued, it became possible to add a level 1

cache to the processor die itself without making the die size unreason-

ably large. Eventually this level 1 cache was split into two caches, one

for holding instructions and one for holding data. This improved