Page 107 - ARM 64 Bit Assembly Language

P. 107

Data processing and other instructions 93

• <op> is one of madd, msub,or mneg.

• <op2> is either mul or mneg. mul is an alias for madd,and mneg is an alias for msub.Both

aliases use the zero register ZR for Ra.

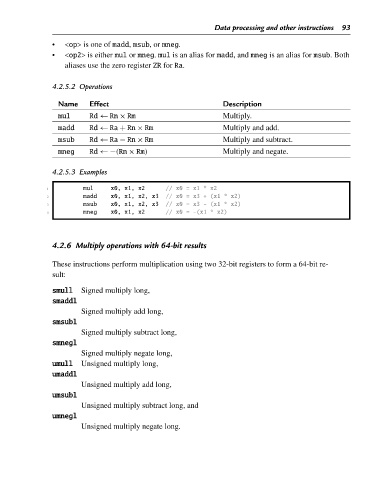

4.2.5.2 Operations

Name Effect Description

mul Rd ← Rn × Rm Multiply.

madd Rd ← Ra + Rn × Rm Multiply and add.

msub Rd ← Ra − Rn × Rm Multiply and subtract.

mneg Rd ←−(Rn × Rm) Multiply and negate.

4.2.5.3 Examples

1 mul x0, x1, x2 // x0 = x1 * x2

2 madd x0, x1, x2, x3 // x0 = x3 + (x1 * x2)

3 msub x0, x1, x2, x3 // x0 = x3 - (x1 * x2)

4 mneg x0, x1, x2 // x0 = -(x1 * x2)

4.2.6 Multiply operations with 64-bit results

These instructions perform multiplication using two 32-bit registers to form a 64-bit re-

sult:

smull Signed multiply long,

smaddl

Signed multiply add long,

smsubl

Signed multiply subtract long,

smnegl

Signed multiply negate long,

umull Unsigned multiply long,

umaddl

Unsigned multiply add long,

umsubl

Unsigned multiply subtract long, and

umnegl

Unsigned multiply negate long.