Page 82 - ARM 64 Bit Assembly Language

P. 82

Load/store and branch instructions 67

1 ldrsh x5, [x0, 8]

Store the least significant byte in w1 at Mem[x9]:

1 strb w1, [x9]

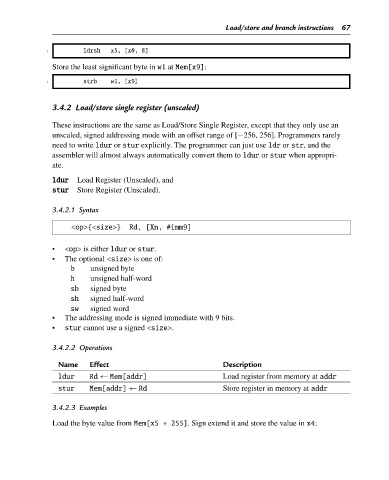

3.4.2 Load/store single register (unscaled)

These instructions are the same as Load/Store Single Register, except that they only use an

unscaled, signed addressing mode with an offset range of [−256, 256]. Programmers rarely

need to write ldur or stur explicitly. The programmer can just use ldr or str,and the

assembler will almost always automatically convert them to ldur or stur when appropri-

ate.

ldur Load Register (Unscaled), and

stur Store Register (Unscaled).

3.4.2.1 Syntax

<op>{<size>} Rd, [Xn, #imm9]

• <op> is either ldur or stur.

• The optional <size> is one of:

b unsigned byte

h unsigned half-word

sb signed byte

sh signed half-word

sw signed word

• The addressing mode is signed immediate with 9 bits.

• stur cannot use a signed <size>.

3.4.2.2 Operations

Name Effect Description

ldur Rd ← Mem[addr] Load register from memory at addr

stur Mem[addr] ← Rd Store register in memory at addr

3.4.2.3 Examples

Load the byte value from Mem[x5 + 255]. Sign extend it and store the value in x4: