Page 8 -

P. 8

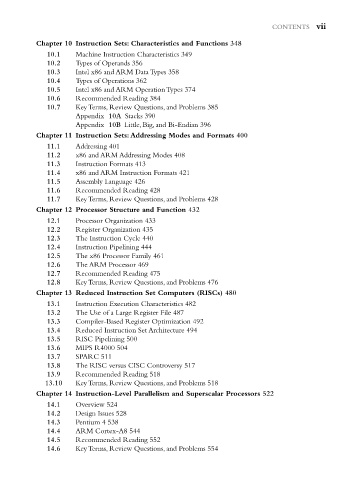

CONTENTS vii

Chapter 10 Instruction Sets: Characteristics and Functions 348

10.1 Machine Instruction Characteristics 349

10.2 Types of Operands 356

10.3 Intel x86 and ARM Data Types 358

10.4 Types of Operations 362

10.5 Intel x86 and ARM Operation Types 374

10.6 Recommended Reading 384

10.7 Key Terms, Review Questions, and Problems 385

Appendix 10A Stacks 390

Appendix 10B Little, Big, and Bi-Endian 396

Chapter 11 Instruction Sets: Addressing Modes and Formats 400

11.1 Addressing 401

11.2 x86 and ARM Addressing Modes 408

11.3 Instruction Formats 413

11.4 x86 and ARM Instruction Formats 421

11.5 Assembly Language 426

11.6 Recommended Reading 428

11.7 Key Terms, Review Questions, and Problems 428

Chapter 12 Processor Structure and Function 432

12.1 Processor Organization 433

12.2 Register Organization 435

12.3 The Instruction Cycle 440

12.4 Instruction Pipelining 444

12.5 The x86 Processor Family 461

12.6 The ARM Processor 469

12.7 Recommended Reading 475

12.8 Key Terms, Review Questions, and Problems 476

Chapter 13 Reduced Instruction Set Computers (RISCs) 480

13.1 Instruction Execution Characteristics 482

13.2 The Use of a Large Register File 487

13.3 Compiler-Based Register Optimization 492

13.4 Reduced Instruction Set Architecture 494

13.5 RISC Pipelining 500

13.6 MIPS R4000 504

13.7 SPARC 511

13.8 The RISC versus CISC Controversy 517

13.9 Recommended Reading 518

13.10 Key Terms, Review Questions, and Problems 518

Chapter 14 Instruction-Level Parallelism and Superscalar Processors 522

14.1 Overview 524

14.2 Design Issues 528

14.3 Pentium 4 538

14.4 ARM Cortex-A8 544

14.5 Recommended Reading 552

14.6 Key Terms, Review Questions, and Problems 554