Page 394 - DSP Integrated Circuits

P. 394

8.9 Shared-Memory Architectures 379

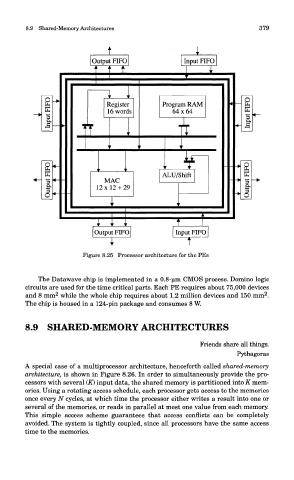

Figure 8.25 Processor architecture for the PEs

The Datawave chip is implemented in a 0.8-um CMOS process. Domino logic

circuits are used for the time critical parts. Each PE requires about 75,000 devices

2

2

and 8 mm while the whole chip requires about 1.2 million devices and 150 mm .

The chip is housed in a 124-pin package and consumes 8 W.

8.9 SHARED-MEMORY ARCHITECTURES

Friends share all things.

Pythagoras

A special case of a multiprocessor architecture, henceforth called shared-memory

architecture, is shown in Figure 8.26. In order to simultaneously provide the pro-

cessors with several (K) input data, the shared memory is partitioned into K mem-

ories. Using a rotating access schedule, each processor gets access to the memories

once every N cycles, at which time the processor either writes a result into one or

several of the memories, or reads in parallel at most one value from each memory.

This simple access scheme guarantees that access conflicts can be completely

avoided. The system is tightly coupled, since all processors have the same access

time to the memories.