Page 399 - DSP Integrated Circuits

P. 399

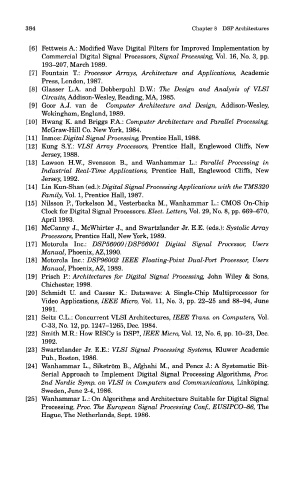

384 Chapter 8 DSP Architectures

[6] Fettweis A.: Modified Wave Digital Filters for Improved Implementation by

Commercial Digital Signal Processors, Signal Processing, Vol. 16, No. 3, pp.

193-207, March 1989.

[7] Fountain T.: Processor Arrays, Architecture and Applications, Academic

Press, London, 1987.

[8] Glasser L.A. and Dobberpuhl D.W.: The Design and Analysis of VLSI

Circuits, Addison-Wesley, Reading, MA, 1985.

[9] Goor A.J. van de Computer Architecture and Design, Addison-Wesley,

Wokingham, England, 1989.

[10] Hwang K. and Briggs F.A.: Computer Architecture and Parallel Processing,

McGraw-Hill Co. New York, 1984.

[11] Inmos: Digital Signal Processing, Prentice Hall, 1988.

[12] Kung S.Y.: VLSI Array Processors, Prentice Hall, Englewood Cliffs, New

Jersey, 1988.

[13] Lawson H.W., Svensson B., and Wanhammar L.: Parallel Processing in

Industrial Real-Time Applications, Prentice Hall, Englewood Cliffs, New

Jersey, 1992.

[14] Lin Kun-Shan (ed.): Digital Signal Processing Applications with the TMS320

Family, Vol. 1, Prentice Hall, 1987.

[15] Nilsson P., Torkelson M., Vesterbacka M., Wanhammar L.: CMOS On-Chip

Clock for Digital Signal Processors. Elect. Letters, Vol. 29, No. 8, pp. 669-670,

April 1993.

[16] McCanny J., McWhirter J., and Swartzlander Jr. E.E. (eds.): Systolic Array

Processors, Prentice Hall, New York, 1989.

[17] Motorola Inc.: DSP560001DSP56001 Digital Signal Processor, Users

Manual, Phoenix, AZ, 1990.

[18] Motorola Inc.: DSP96002 IEEE Floating-Point Dual-Port Processor, Users

Manual, Phoenix, AZ, 1989.

[19] Prisch P.: Architectures for Digital Signal Processing, John Wiley & Sons,

Chichester, 1998.

[20] Schmidt U. and Caesar K: Datawave: A Single-Chip Multiprocessor for

Video Applications, IEEE Micro, Vol. 11, No. 3, pp. 22-25 and 88-94, June

1991.

[21] Seitz C.L.: Concurrent VLSI Architectures, IEEE Trans, on Computers, Vol.

C-33, No. 12, pp. 1247-1265, Dec. 1984.

[22] Smith M.R.: How RISCy is DSP?, IEEE Micro, Vol. 12, No. 6, pp. 10-23, Dec.

1992.

[23] Swartzlander Jr. E.E.: VLSI Signal Processing Systems, Kluwer Academic

Pub., Boston, 1986.

[24] Wanhammar L., Sikstrom B., Afghani M., and Pencz J.: A Systematic Bit-

Serial Approach to Implement Digital Signal Processing Algorithms, Proc.

2nd Nordic Symp. on VLSI in Computers and Communications, Linkoping,

Sweden, June 2-4,1986.

[25] Wanhammar L.: On Algorithms and Architecture Suitable for Digital Signal

Processing, Proc. The European Signal Processing Conf, EUSIPCO-86, The

Hague, The Netherlands, Sept. 1986.