Page 192 - Hardware Implementation of Finite-Field Arithmetic

P. 192

m

Operations over GF (2 )—Polynomial Bases 173

An executable Ada file LSBfirst.adb, including Algorithm 7.3, is

available at www.arithmetic-circuits.org. It can be observed that

Algorithm 7.3 is the binary version of the LSE-first multiplier given in

Algorithm 5.7. It is also important to note that in the MSB- and LSB-

first multiplication schemes, several coefficients could be processed

at each step.

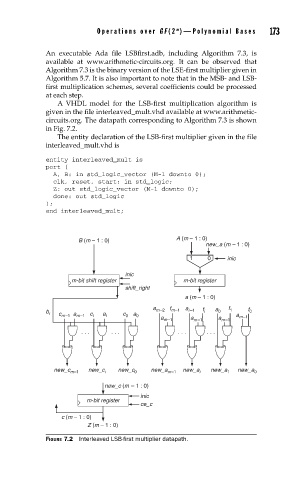

A VHDL model for the LSB-first multiplication algorithm is

given in the file interleaved_mult.vhd available at www.arithmetic-

circuits.org. The datapath corresponding to Algorithm 7.3 is shown

in Fig. 7.2.

The entity declaration of the LSB-first multiplier given in the file

interleaved_mult.vhd is

entity interleaved_mult is

port (

A, B: in std_logic_vector (M-1 downto 0);

clk, reset, start: in std_logic;

Z: out std_logic_vector (M-1 downto 0);

done: out std_logic

);

end interleaved_mult;

B (m – 1 : 0) A (m – 1 : 0)

new_a (m – 1 : 0)

1 0 inic

inic

m-bit shift register m-bit register

shift_right

a (m – 1 : 0)

a m–2 f m–1 a i –1 f i a 0 f 1 f 0

b i

c m–1 a m–1 c i a i c 0 a 0 a m–1

a m–1 a m–1 a m–1

. . . . . . . . . . . .

new_c m–1 new_c i new_c 0 new_a m–1 new_a i new_a 1 new_a 0

new_c (m – 1 : 0)

inic

m-bit register

ce_c

c (m – 1 : 0)

Z (m – 1 : 0)

FIGURE 7.2 Interleaved LSB-fi rst multiplier datapath.