Page 272 - Mathematical Techniques of Fractional Order Systems

P. 272

Design of Fractional Order Fuzzy Sliding Mode Controller Chapter | 9 261

_

ð

V 52 s Eφ 1 ksÞ ð9:58Þ

As, s . 0 as well as Eφ 1 ks . 0

_

V 52 s Eφ 1 ksÞ , 0 ð9:59Þ

ð

_

Eq. (9.59) shows that V , 0 which states that the designed controller for

exponential law will be stable for s . 0.

Case II: When s , 0 then sat sðÞ , 0

Let sat sðÞ 52 φ, where, φ . 0.

From (9.56)

_

ð

V 5 s Eφ 2 ksÞ ð9:60Þ

Let, Ω 52 s such that Ω . 0

Now from (9.59),

_

ð

V 52 Ω Eφ 1 kΩÞ ð9:61Þ

_

Since; Ω Eφ 1 kΩÞ . 0; V 52 Ω Eφ 1 kΩÞ , 0 ð9:62Þ

ð

ð

_

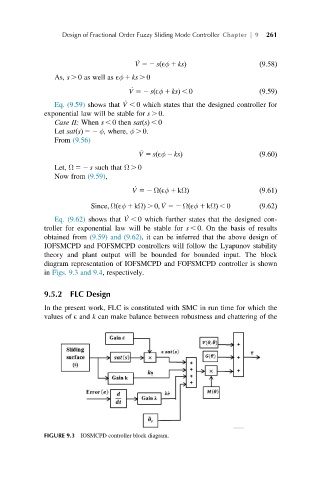

Eq. (9.62) shows that V , 0 which further states that the designed con-

troller for exponential law will be stable for s , 0. On the basis of results

obtained from (9.59) and (9.62), it can be inferred that the above design of

IOFSMCPD and FOFSMCPD controllers will follow the Lyapunov stability

theory and plant output will be bounded for bounded input. The block

diagram representation of IOFSMCPD and FOFSMCPD controller is shown

in Figs. 9.3 and 9.4, respectively.

9.5.2 FLC Design

In the present work, FLC is constituted with SMC in run time for which the

values of E and k can make balance between robustness and chattering of the

FIGURE 9.3 IOSMCPD controller block diagram.