Page 35 - PDA Robotics Using Your Personal Digital Assistant to Control Your Robot

P. 35

PDA 01 5/30/03 9:09 AM Page 12

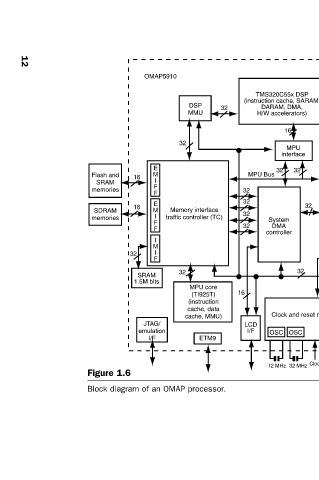

DSP public peripherals

private peripherals

timers (3)

DSP

peripheral bus

DSP private

TMS320C55x DSP Watchdog timer 16 level 1/2 McBSP1 interrupt handlers (instruction cache, SARAM, DARAM, DMA, McBSP3 DSP public (shared) peripheral bus H/W accelerators) MCSI1 MCSI2 16 16 MPU/DSP shared peripherals Mailbox MPU GPIO I/F interface UART1 TIPB UART2 32 32 switch UART3 IrDA MPU public peripherals MPU McBSP2 peripheral 32 bridge USB Host I/F MPU public System peripherals bus 32 USB Function I/F DMA controller I 2 C µWire Camera I/F MPUIO 32

MPU Bus

32

32

32

32

16 LCD I/F

32

DSP MMU Memory interface traffic controller (TC) MPU core (TI925T) (instruction cache, data cache, MMU) ETM9

32 32

OMAP5910 E M I F F E M I F F I M I F JTAG/ emulation I/F Block diagram of an OMAP processor.

16 16 32 SRAM 1.5M bits

Flash and SRAM memories SDRAM memories Figure 1.6

12