Page 69 - The Art of Designing Embedded Systems

P. 69

56 THE ART OF DESIGNING EMBEDDED SYSTEMS

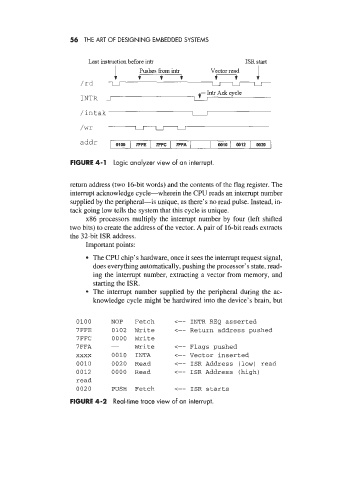

Last instruction before intr ISR start

Pushes from intr Vector read

m

/ rd U U

INTR i

/intak

/wr U U U

0100 7FFE 7FFC 7FFA I 0010 1 0012 I 0020

FIGURE 4-1 Logic analyzer view of an interrupt.

return address (two 16-bit words) and the contents of the flag register. The

interrupt acknowledge cycle-wherein the CPU reads an interrupt number

supplied by the peripheral-is unique, as there’s no read pulse. Instead, in-

tack going low tells the system that this cycle is unique.

x86 processors multiply the interrupt number by four (left shifted

two bits) to create the address of the vector. A pair of 16-bit reads extracts

the 32-bit ISR address.

Important points:

The CPU chip’s hardware, once it sees the interrupt request signal,

does everything automatically, pushing the processor’s state, read-

ing the interrupt number, extracting a vector from memory, and

starting the ISR.

The interrupt number supplied by the peripheral during the ac-

knowledge cycle might be hardwired into the device’s brain, but

0100 NOP Fetch <-- INTR REQ asserted

7FFE 0102 Write <-- Return address pushed

7FFC 0000 Write

7FFA - Write <-- Flags pushed

xxxx 0010 INTA <-- Vector inserted

0010 0020 Read <-- ISR Address (low) read

0012 0000 Read <-- ISR Address (high)

read

0020 PUSH Fetch <-- ISR starts

FIGURE 4-2 Real-time trace view of an interrupt.