Page 339 - ARM 64 Bit Assembly Language

P. 339

Advanced SIMD instructions 329

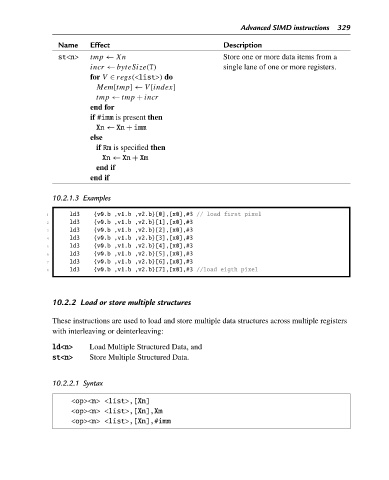

Name Effect Description

st<n> tmp ← Xn Store one or more data items from a

incr ← byteSize(T) single lane of one or more registers.

for V ∈ regs(<list>) do

Mem[tmp]← V [index]

tmp ← tmp + incr

end for

if #imm is present then

Xn ← Xn + imm

else

if Rm is specified then

Xn ← Xn + Xm

end if

end if

10.2.1.3 Examples

1 ld3 {v0.b ,v1.b ,v2.b}[0],[x0],#3 // load first pixel

2 ld3 {v0.b ,v1.b ,v2.b}[1],[x0],#3

3 ld3 {v0.b ,v1.b ,v2.b}[2],[x0],#3

4 ld3 {v0.b ,v1.b ,v2.b}[3],[x0],#3

5 ld3 {v0.b ,v1.b ,v2.b}[4],[x0],#3

6 ld3 {v0.b ,v1.b ,v2.b}[5],[x0],#3

7 ld3 {v0.b ,v1.b ,v2.b}[6],[x0],#3

8 ld3 {v0.b ,v1.b ,v2.b}[7],[x0],#3 //load eigth pixel

10.2.2 Load or store multiple structures

These instructions are used to load and store multiple data structures across multiple registers

with interleaving or deinterleaving:

ld<n> Load Multiple Structured Data, and

st<n> Store Multiple Structured Data.

10.2.2.1 Syntax

<op><n> <list>,[Xn]

<op><n> <list>,[Xn],Xm

<op><n> <list>,[Xn],#imm