Page 343 - ARM 64 Bit Assembly Language

P. 343

Advanced SIMD instructions 333

10.3 Data movement instructions

With the additional register views added by Advanced SIMD, there are many more ways to

specify data movement. Instructions are provided to move data using the Advanced SIMD

views, the FP/NEON views, and the AArch64 integer register views. This results in a large

number of possible move instructions.

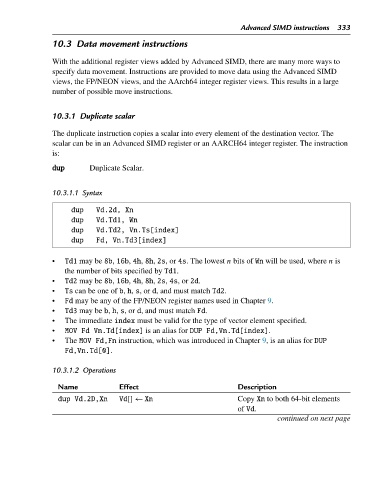

10.3.1 Duplicate scalar

The duplicate instruction copies a scalar into every element of the destination vector. The

scalar can be in an Advanced SIMD register or an AARCH64 integer register. The instruction

is:

dup Duplicate Scalar.

10.3.1.1 Syntax

dup Vd.2d, Xn

dup Vd.Td1, Wn

dup Vd.Td2, Vn.Ts[index]

dup Fd, Vn.Td3[index]

• Td1 may be 8b, 16b, 4h, 8h, 2s,or 4s.The lowest n bits of Wn will be used, where n is

the number of bits specified by Td1.

• Td2 may be 8b, 16b, 4h, 8h, 2s, 4s,or 2d.

• Ts can be one of b, h, s,or d, and must match Td2.

• Fd may be any of the FP/NEON register names used in Chapter 9.

• Td3 may be b, h, s,or d, and must match Fd.

• The immediate index must be valid for the type of vector element specified.

• MOV Fd Vn.Td[index] is an alias for DUP Fd,Vn.Td[index].

• The MOV Fd,Fn instruction, which was introduced in Chapter 9, is an alias for DUP

Fd,Vn.Td[0].

10.3.1.2 Operations

Name Effect Description

dup Vd.2D,Xn Vd[] ← Xn Copy Xn to both 64-bit elements

of Vd.

continued on next page