Page 78 - ARM Based Microcontroller Projects Using MBED

P. 78

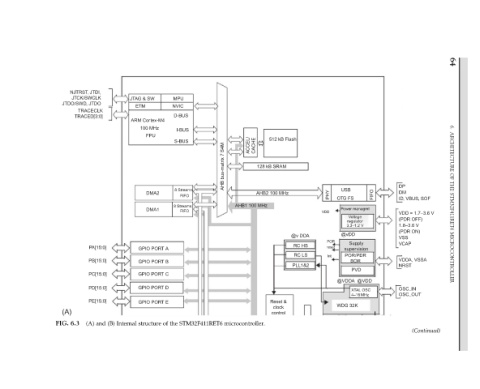

64 6. ARCHITECTURE OF THE STM32F411RET6 MICROCONTROLLER

ID, VBUS, SOF VDD = 1.7–3.6 V (PDR OFF) (PDR ON) VDDA, VSSA OSC_OUT (Continued)

DP DM 1.8–3.6 V VSS VCAP NRST OSC_IN

FIFO

Power managmt Voltage regulator 3.3–1.2 V Supply supervision POR/PDR BOR PVD @VDD XTAL OSC 4–16 MHz

USB OTG FS @vDD @VDDA WDG 32K

POR reset Int

VDD

PHY

@v DDA RC HS RC LS PLL1&2

512 kB Flash 128 kB SRAM AHB2 100 MHz Reset & clock control

AHB1 100 MHz microcontroller.

CACHE

ACCEL/

STM32F411RET6

AHB bus-matrix 7 S4M

MPU NVIC D-BUS I-BUS S-BUS 8 Streams FIFO 8 Streams FIFO the of

JTAG & SW ETM ARM Cortex-M4 100 MHz FPU DMA2 DMA1 GPIO PORT A GPIO PORT B GPIO PORT C GPIO PORT D GPIO PORT E structure

Internal

(B) and

NJTRST , JTDI, JTCK/SWCLK JTDO/SWD, JTDO TRACECLK TRACED[3:0] PA[15:0] PB[15:0] PC[15:0] PD[15:0] PE[15:0] (A) (A) 6.3 FIG.