Page 575 - DSP Integrated Circuits

P. 575

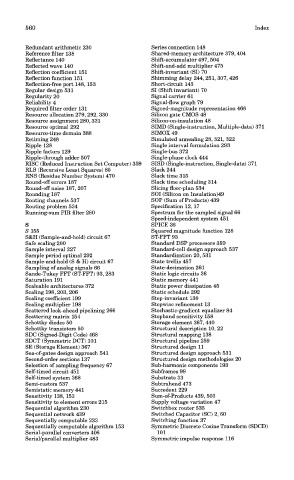

560 Index

Redundant arithmetic 230 Series connection 148

Reference filter 138 Shared-memory architecture 379,404

Reflectance 140 Shift-accumulator 497, 504

Reflected wave 140 Shift-and-add multiplier 475

Reflection coefficient 151 Shift-invariant (SI) 70

Reflection function 151 Shimming delay 244, 251, 307, 426

Reflection-free port 148,153 Short-circuit 145

Regular design 531 SI (Shift invariant) 70

Regularity 20 Signal carrier 61

Reliability 4 Signal-flow graph 79

Required filter order 131 Signed-magnitude representation 468

Resource allocation 279,292, 330 Silicon gate CMOS 48

Resource assignment 280, 331 Silicon-on-insulation 48

Resource optimal 292 SIMD (Single-instruction, Multiple-data) 371

Resource-time domain 388 SIMOX 49

Retiming 248 Simulated annealing 28, 321, 322

Ripple 128 Single interval formulation 293

Ripple factors 129 Single-bus 372

Ripple-through adder 507 Single-phase clock 444

RISC (Reduced Instruction Set Computer) 359 SISD (Single-instruction, Single-data) 371

RLS (Recursive Least Squares) 85 Slack 244

RNS (Residue Number System) 470 Slack time 315

Round-off errors 187 Slack time scheduling 314

Round-off noise 187, 207 Slicing floor-plan 534

Rounding 187 SOI (Silicon on Insulation)49

Routing channels 537 SOP (Sum of Products) 439

Routing problem 534 Specification 12, 17

Running-sum FIR filter 280 Spectrum for the sampled signal 66

Speed-independent system 451

S SPICE 36

S 155 Squared magnitude function 128

S&H (Sample-and-hold) circuit 67 ST-FFT 93

Safe scaling 200 Standard DSP processors 359

Sample interval 227 Standard-cell design approach 537

Sample period optimal 292 Standardization 20, 531

Sample-and-hold (S & H) circuit 67 State trellis 457

Sampling of analog signals 66 State-decimation 261

Sande-Tukey FFT (ST-FFT) 93, 283 Static logic circuits 36

Saturation 191 Static memory 441

Scaleable architectures 372 Static power dissipation 45

Scaling 198, 203, 206 Static schedule 292

Scaling coefficient 199 Step-invariant 130

Scaling multiplier 198 Stepwise refinement 13

Scattered look-ahead pipelining 266 Stochastic-gradient equalizer 84

Scattering matrix 154 Stopband sensitivity 158

Schottky diodes 50 Storage element 367, 440

Schottky transistors 50 Structural description 10, 22

SDC (Signed-Digit Code) 468 Structural mapping 138

SDCT (Symmetric DCT) 101 Structural pipeline 259

SE (Storage Element) 367 Structured design 11

Sea-of-gates design approach 541 Structured design approach 531

Second-order sections 137 Structured design methodologies 20

Selection of sampling frequency 67 Sub-harmonic components 193

Self-timed circuit 451 Subframes 99

Self-timed system 368 Substrate 33

Semi-custom 537 Subtrahend 473

Semistatic memory 441 Succedent 229

Sensitivity 138,153 Sum-of-Products 439, 503

Sensitivity to element errors 215 Supply voltage variation 47

Sequential algorithm 230 Switchbox router 535

Sequential network 439 Switched Capacitor (SC) 2, 60

Sequentially computable 233 Switching function 37

Sequentially computable algorithm 153 Symmetric Discrete Cosine Transform (SDCD)

Serial-parallel converters 406 101

Serial/parallel multiplier 483 Symmetric impulse response 116