Page 573 - DSP Integrated Circuits

P. 573

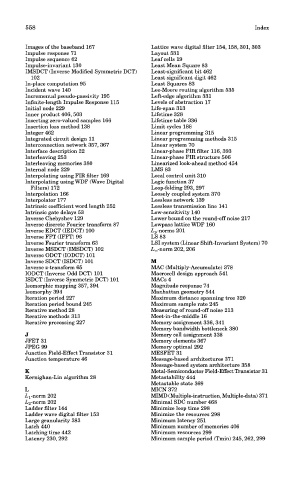

558 Index

Images of the baseband 167 Lattice wave digital filter 154,158, 301, 303

Impulse response 71 Layout 531

Impulse sequence 62 Leaf cells 19

Impulse-invariant 130 Least Mean Square 83

IMSDCT (Inverse Modified Symmetric DCT) Least-significant bit 462

102 Least significant digit 462

In-place computation 95 Least Squares 83

Incident wave 140 Lee-Moore routing algorithm 535

Incremental pseudo-passivity 195 Left-edge algorithm 331

Infinite-length Impulse Response 115 Levels of abstraction 17

Initial node 229 Life-span 313

Inner product 406, 503 Lifetime 328

Inserting zero-valued samples 166 Lifetime table 336

Insertion loss method 138 Limit cycles 188

Integer 462 Linear programming 315

Integrated circuit design 11 Linear programming methods 315

Interconnection network 357, 367 Linear system 70

Interface description 22 Linear-phase FIR filter 116, 393

Interleaving 253 Linear-phase FIR structure 506

Interleaving memories 380 Linearized look-ahead method 454

Internal node 229 LMS 83

Interpolating using FIR filter 169 Local control unit 310

Interpolating using WDF (Wave Digital Logic function 37

Filters) 172 Loop-folding 293, 297

Interpolation 166 Loosely coupled system 370

Interpolator 177 Lossless network 139

Intrinsic coefficient word length 252 Lossless transmission line 141

Intrinsic gate delays 53 Low-sensitivity 140

Inverse Chebyshev 129 Lower bound on the round-off noise 217

Inverse discrete Fourier transform 87 Lowpass lattice WDF 160

Inverse EDCT (IEDCT) 100 L p-norms 201

Inverse FFT (IFFT) 96 LS 83

Inverse Fourier transform 63 LSI system (Linear Shift-Invariant System) 70

Inverse MSDCT (IMSDCT) 102 L^-norm 202, 206

Inverse ODCT (IODCT) 101

Inverse SDCT (ISDCT) 101 M

Inverse z-transform 65 MAC (Multiply-Accumulate) 378

IODCT (Inverse Odd DCT) 101 Macrocell design approach 541

ISDCT (Inverse Symmetric DCT) 101 MACs 4

Isomorphic mapping 357, 394 Magnitude response 74

Isomorphy 394 Manhattan geometry 544

Iteration period 227 Maximum distance spanning tree 320

Iteration period bound 245 Maximum sample rate 245

Iterative method 28 Measuring of round-off noise 213

Iterative methods 313 Meet-in-the-middle 16

Iterative processing 227 Memory assignment 336, 341

Memory bandwidth bottleneck 380

J Memory cell assignment 338

JFET 31 Memory elements 367

JPEG 99 Memory optimal 292

Junction Field-Effect Transistor 31 MESFET 31

Junction temperature 46 Message-based architectures 371

Message-based system architecture 358

K Metal-Semiconductor Field-Effect Transistor 31

Kernighan-Lin algorithm 28 Metastability 444

Metastable state 369

L MICN 372

L !-norm 202 MIMD (Multiple-instruction, Multiple-data) 371

L 2-norm 202 Minimal SDC number 468

Ladder filter 144 Minimize loop time 298

Ladder wave digital filter 153 Minimize the resources 298

Large granularity 383 Minimum latency 251

Latch 440 Minimum number of memories 406

Latching time 442 Minimum resources 299

Latency 230, 292 Minimum sample period (Tmin) 245, 262, 299