Page 568 - DSP Integrated Circuits

P. 568

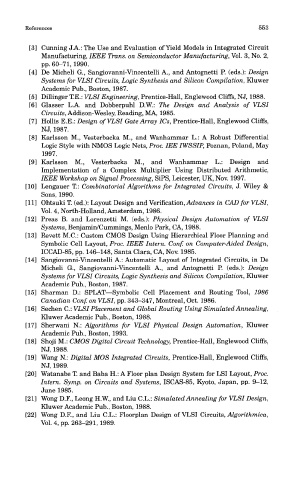

References 553

[3] Cunning J.A.: The Use and Evaluation of Yield Models in Integrated Circuit

Manufacturing, IEEE Trans, on Semiconductor Manufacturing, Vol. 3, No. 2,

pp. 60-71, 1990.

[4] De Micheli G., Sangiovanni-Vincentelli A., and Antognetti P. (eds.): Design

Systems for VLSI Circuits, Logic Synthesis and Silicon Compilation, Kluwer

Academic Pub., Boston, 1987.

[5] Dillinger T.E.: VLSI Engineering, Prentice-Hall, Englewood Cliffs, NJ, 1988.

[6] Glasser L.A. and Dobberpuhl D.W.: The Design and Analysis of VLSI

Circuits, Addison-Wesley, Reading, MA, 1985.

[7] Hollis E.E.: Design of VLSI Gate Array ICs, Prentice-Hall, Englewood Cliffs,

NJ, 1987.

[8] Karlsson M., Vesterbacka M., and Wanhammar L.: A Robust Differential

Logic Style with NMOS Logic Nets, Proc. IEEIWSSIP, Poznan, Poland, May

1997.

[9] Karlsson M., Vesterbacka M., and Wanhammar L.: Design and

Implementation of a Complex Multiplier Using Distributed Arithmetic,

IEEE Workshop on Signal Processing, SiPS, Leicester, UK, Nov. 1997.

[10] Lengauer T.: Combinatorial Algorithms for Integrated Circuits, J. Wiley &

Sons, 1990.

[11] Ohtsuki T. (ed.): Layout Design and Verification, Advances in CAD for VLSI,

Vol. 4, North-Holland, Amsterdam, 1986.

[12] Preas B. and Lorenzetti M. (eds.): Physical Design Automation of VLSI

Systems, Benjamin/Cummings, Menlo Park, CA, 1988.

[13] Revett M.C.: Custom CMOS Design Using Hierarchical Floor Planning and

Symbolic Cell Layout, Proc. IEEE Intern. Conf. on Computer-Aided Design,

ICCAD-85, pp. 146-148, Santa Clara, CA, Nov. 1985.

[14] Sangiovanni-Vincentelli A.: Automatic Layout of Integrated Circuits, in De

Micheli G., Sangiovanni-Vincentelli A., and Antognetti P. (eds.): Design

Systems for VLSI Circuits, Logic Synthesis and Silicon Compilation, Kluwer

Academic Pub., Boston, 1987.

[15] Sharman D.: SPLAT—Symbolic Cell Placement and Routing Tool, 1986

Canadian Conf. on VLSI, pp. 343-347, Montreal, Oct. 1986.

[16] Sechen C.: VLSI Placement and Global Routing Using Simulated Annealing,

Kluwer Academic Pub., Boston, 1988.

[17] Sherwani N: Algorithms for VLSI Physical Design Automation, Kluwer

Academic Pub., Boston, 1993.

[18] Shoji M.: CMOS Digital Circuit Technology, Prentice-Hall, Englewood Cliffs,

NJ, 1988.

[19] Wang N: Digital MOS Integrated Circuits, Prentice-Hall, Englewood Cliffs,

NJ, 1989.

[20] Watanabe T. and Baba H.: A Floor plan Design System for LSI Layout, Proc.

Intern. Symp. on Circuits and Systems, ISCAS-85, Kyoto, Japan, pp. 9-12,

June 1985.

[21] Wong D.F., Leong H.W., and Liu C.L.: Simulated Annealing for VLSI Design,

Kluwer Academic Pub., Boston, 1988.

[22] Wong D.F., and Liu C.L.: Floorplan Design of VLSI Circuits, Algorithmica,

Vol. 4, pp. 263-291,1989.