Page 572 - DSP Integrated Circuits

P. 572

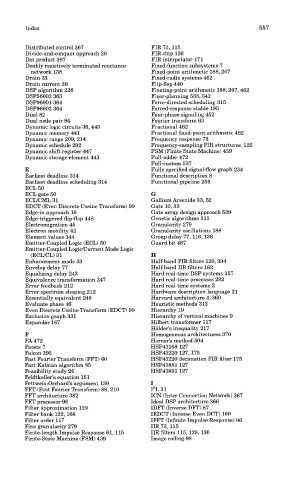

Index 55

Distributed control 367 FIR 73, 115

Divide-and-conquer approach 20 FIR chip 126

Dot product 397 FIR interpolator 171

Doubly resistively terminated reactance Fixed-function subsystems 7

network 138 Fixed-point arithmetic 188, 207

Drain 33 Fixed-radix systems 462

Drain current 36 Flip-flop 440

DSP algorithm 226 Floating-point arithmetic 188, 207, 462

DSP56002 363 Floor-planning 533, 542

DSP96001 364 Force-directed scheduling 315

DSP96002 364 Forced-response stable 195

Dual 82 Four-phase signaling 452

Dual node pair 94 Fourier transform 63

Dynamic logic circuits 36,443 Fractional 462

Dynamic memory 441 Fractional fixed-point arithmetic 462

Dynamic range 209, 214 Frequency response 73

Dynamic schedule 292 Frequency-sampling FIR structures. 126

Dynamic shift register 447 FSM (Finite State Machine) 439

Dynamic storage element 443 Full-adder 472

Full-custom 537

E Fully specified signal-flow graph 234

Earliest deadline 314 Functional description 8

Earliest deadline scheduling 314 Functional pipeline 259

ECL50

ECL gate 50 G

ECL/CML 31 Gallium Arsenide 33, 52

EDCT (Even Discrete Cosine Transform) 99 Gate 10, 33

Edge-in approach 16 Gate array design approach 539

Edge-triggered flip-flop 448 Genetic algorithms 313

Electromigration 45 Granularity 279

Electron mobility 42 Granularity oscillations 188

Element values 144 Group delay 77,116,136

Emitter-Coupled Logic (ECL) 50 Guard bit 487

Emitter-Coupled Logic/Current Mode Logic

(ECL/CL) 31 H

Enhancement mode 33 Half-band FIR filters 120, 394

Envelop delay 77 Half-band IIR filters 162

Equalizing delay 243 Hard real-time DSP systems 357

Equivalence transformation 247 Hard real-time processes 292

Error feedback 212 Hard real-time systems 2

Error spectrum shaping 212 Hardware description language 21

Essentially equivalent 248 Harvard architecture 4, 360

Evaluate phase 46 Heuristic methods 313

Even Discrete Cosine Transform (EDCT) 99 Hierarchy 19

Exclusion graph 331 Hierarchy of vertical machines 9

Expander 167 Hilbert transformer 117

Holder's inequality 217

F Homogeneous architectures 370

FA 472 Horner's method 504

Facets 7 HSP43168 127

Falcon 395 HSP43220 127, 175

Fast Fourier Transform (FFT) 60 HSP43220 decimation FIR filter 175

Fast Kalman algorithm 85 HSP43881 127

Feasibility study 26 HSP43891 127

Feldtkeller's equation 151

Fettweis-Orchard's argument 139 I

2

FFT (Fast Fourier Transform) 88, 210 I L 31

FFT architecture 382 ICN (Inter Connection Network) 367

FFT processor 96 Ideal DSP architecture 366

Filter approximation 129 IDFT (Inverse DFT) 87

Filter bank 122,166 IEDCT (Inverse Even DCT) 100

Filter order 117 IFFT (Infinite Impulse Response) 96

Fine granularity 279 IIR 73,115

Finite-length Impulse Response 61,115 IIR filters 115, 128, 130

Finite-State Machine (FSM) 439 Image coding 98