Page 570 - DSP Integrated Circuits

P. 570

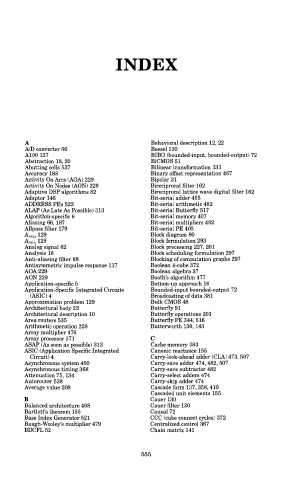

INDEX

A Behavioral description 12, 22

A/D converter 66 Bessel 130

A100 127 BIBO (bounded-input, bounded-output) 72

Abstraction 18, 20 BiCMOS 51

Abutting cells 537 Bilinear transformation 131

Accuracy 188 Binary offset representation 467

Activity On Arcs (AOA) 229 Bipolar 31

Activity On Nodes (AON) 229 Bireciprocal filter 162

Adaptive DSP algorithms 82 Bireciprocal lattice wave digital filter 162

Adaptor 146 Bit-serial adder 455

ADDRESS PEs 522 Bit-serial arithmetic 482

ALAP (As Late As Possible) 313 Bit-serial Butterfly 517

Algorithm-specific 6 Bit-serial memory 407

Aliasing 66,187 Bit-serial multipliers 482

Allpass filter 179 Bit-serial PE 405

A max 129 Block diagram 80

A min 129 Block formulation 293

Analog signal 62 Block processing 227, 261

Analysis 18 Block scheduling formulation 297

Anti-aliasing filter 68 Blocking of computation graphs 297

Antisymmetric impulse response 117 Boolean 4-cube 372

AOA 229 Boolean algebra 37

AON 229 Booth's algorithm 477

Application-specific 5 Bottom-up approach 16

Application-Specific Integrated Circuits Bounded-input bounded-output 72

(ASIC) 4 Broadcasting of data 381

Approximation problem 129 Bulk CMOS 48

Architectural body 23 Butterfly 91

Architectural description 10 Butterfly operations 201

Area routers 535 Butterfly PE 344, 516

Arithmetic operation 228 Butterworth 130,143

Array multiplier 476

Array processor 371 C

ASAP (As soon as possible) 313 Cache memory 383

ASIC (Application Specific Integrated Canonic reactance 155

Circuit) 4 Carry-look-ahead adder (CLA) 473, 507

Asynchronous system 450 Carry-save adder 474, 482, 507

Asynchronous timing 368 Carry-save subtracter 482

Attenuation 75,134 Carry-select adders 474

Autorouter 538 Carry-skip adder 474

Average value 208 Cascade form 137, 358, 410

Cascaded unit elements 155

B Cauer130

Balanced architecture 408 Cauer filter 130

Bartlett's theorem 155 Causal 72

Base Index Generator 521 CCC (cube connect cycles) 372

Baugh-Wooley's multiplier 479 Centralized control 367

BDCFL 52 Chain matrix 141

555