Page 357 - Embedded Microprocessor Systems Real World Design

P. 357

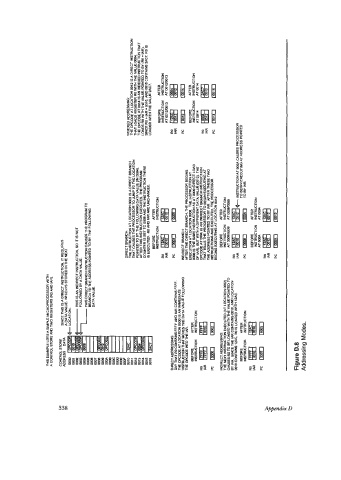

W4S EXAMPLE USES A SIMRE MICROPROCESSOR WITH

A CONTROL STORE AND TWO REGISTERS (RO AND IAR)

01

01 kc:; SINCE THIS IS A DIRECT INSTRUCTION. ITREQUIRES

ot, A DATA VALUE. WHICH IS STORED IN THE NEXl

ww 0- LOCATION.

C6-31

ow2 MIS IS AN INDIRECT INSTRUCTION, SO IT IS NOT

Oom FOLLOWED BY A DATA VALVE.

ooo4

ooo5 TmS DIRECT BRANCH INSTRUCTION CAUSES ME PROGRAM TO

BRANCH To THE ADDRESS POINTED TO BY ME FOLLOWING

wo1

ow7 DATA VALUE.

wo1

oooe

WOA

oore

woc

OWD

WOE

MXF DIRECT BRANCH

WlO

w11 THE INSTRUCTION AT LOCAllON ooo3 IS A DIRECT BRANCH

WT CAUSES THE PROCESSOR TO JUMP TO THE LOCATION

WIZ POINTED TO BY ME FOLLOWING DATA VALUE (IN W).

0013 AFTER THIS INSTRUCTION EXECUTES. THE PROORAM

0014 COLJNER IS SET TO WOE AM) THE INSTRUCTION THERE

W15

001s IS EXECUTED. RO AND IAR ARE UNCHANGED.

BEFORE AFTER

INSTRUCTION INSTRUCTION

BEFORE AFTER

INSTRUCTION INSTRUCTION

AT WIUa13 AT WlzmO13

DmRECT AODDRESSIffi

SAY THAT RO CONTAINS FFFF AND IAR CONTAINS f FFF

THL: OPCODE AT LDCATION Oooa IS AN IMMEDIATE

IkSTRIXTlON THAT MOMS THE DATA VALUE FOCLOWING INDIRECT BRANCH:

mE OFCODE INTO THE IAR AFTER TM DIRECT BRANCH. THE PROCESSOR BEGINS

EXECUTION AT LOCATION ooo8. THE INSTRUCTION AT BEFORE AFTER

mo8 IS THE SAME INSTRUCTION AS AT WW (DIRECT LOAD INSTRUCTION INSTRUCTION

OF IARI. BW WITH A DIFFERENT DATA VALUE iOO12I. THE AT W14 AT W14

OFCodE AT MOA IS AN INDIRECT BRANCH INSklJt%ON

THAT TELLS M PROCESSOR TO BEGIN OeCUTlNG AT

THE ADDRESS POINTED TO BY IAR AFTER WSE TWO

INSlRUCTONS ARE EXECUTED. THE PROCESSOR

BEGINS u(ECUTIffi AT LOCATION 0012

INDIRECT ADDRESSING ' BEFORE

ME Nu(T INSTRUCTION EXECUTED (AT LOCATIONWZ) INSTRUCTION

CAUSES ROTO BE LOADED WITH THE VALUE WINTED TO AT mDBMMe

BY IAR. SINCE THE IAR CONTAINS WID. AND LOCATION

0010 CONTAINS lac. RO IS LOADED wim iac

0- INSTRUCTION AT WOA CAUSES PROCESSSOR

TO BEGIN EJECIXING AT ADDRESS POINTED

ErawB7 100(141 TOBYIAR

BEFORE AFTER

INSTRUCTION INSTRUCTION

AT axU AT OmA

ER

=rww 100111

b

Figure D.8

Addressing Modes.