Page 147 - Hardware Implementation of Finite-Field Arithmetic

P. 147

130 Cha pte r F i v e

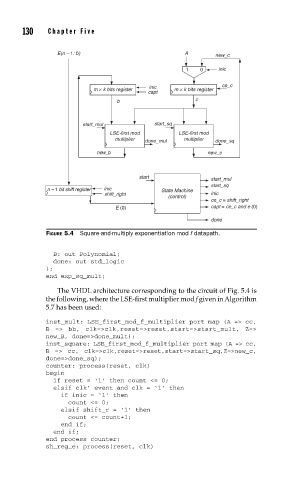

E(n – 1: 0) A

new_c

1 0 inic

inic ce_c

m × k bits register m × k bits register

capt

c

b

start_mul start_sq

LSE-first mod LSE-first mod

multiplier done_mul multiplier done_sq

new_b new_c

start start_mul

start_sq

n – 1 bit shift register inic State Machine

shift_right inic

(control)

ce_c = shift_right

E (0) capt = ce_c and e (0)

done

FIGURE 5.4 Square-and-multiply exponentiation mod f datapath.

B: out Polynomial;

done: out std_logic

);

end exp_sq_mult;

The VHDL architecture corresponding to the circuit of Fig. 5.4 is

the following, where the LSE-first multiplier mod f given in Algorithm

5.7 has been used:

inst_mult: LSE_first_mod_f_multiplier port map (A => cc,

B => bb, clk=>clk,reset=>reset,start=>start_mult, Z=>

new_B, done=>done_mult);

inst_square: LSE_first_mod_f_multiplier port map (A => cc,

B => cc, clk=>clk,reset=>reset,start=>start_sq,Z=>new_c,

done=>done_sq);

counter: process(reset, clk)

begin

if reset = ‘1’ then count <= 0;

elsif clk’ event and clk = ‘1’ then

if inic = ‘1’ then

count <= 0;

elsif shift_r = ‘1’ then

count <= count+1;

end if;

end if;

end process counter;

sh_reg_e: process(reset, clk)