Page 148 - Hardware Implementation of Finite-Field Arithmetic

P. 148

Operations over Z [ x ]/ f ( x ) 131

p

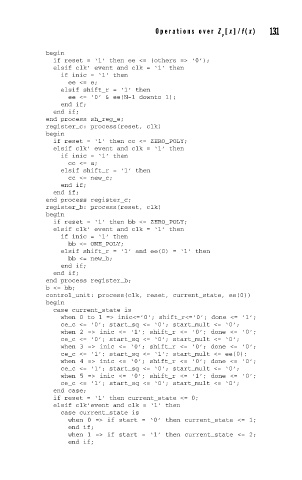

begin

if reset = ‘1’ then ee <= (others => ‘0’);

elsif clk’ event and clk = ‘1’ then

if inic = ‘1’ then

ee <= e;

elsif shift_r = ‘1’ then

ee <= ‘0’ & ee(N-1 downto 1);

end if;

end if;

end process sh_reg_e;

register_c: process(reset, clk)

begin

if reset = ‘1’ then cc <= ZERO_POLY;

elsif clk’ event and clk = ‘1’ then

if inic = ‘1’ then

cc <= a;

elsif shift_r = ‘1’ then

cc <= new_c;

end if;

end if;

end process register_c;

register_b: process(reset, clk)

begin

if reset = ‘1’ then bb <= ZERO_POLY;

elsif clk’ event and clk = ‘1’ then

if inic = ‘1’ then

bb <= ONE_POLY;

elsif shift_r = ‘1’ and ee(0) = ‘1’ then

bb <= new_b;

end if;

end if;

end process register_b;

b <= bb;

control_unit: process(clk, reset, current_state, ee(0))

begin

case current_state is

when 0 to 1 => inic<=’0’; shift_r<=’0’; done <= ‘1’;

ce_c <= ‘0’; start_sq <= ‘0’; start_mult <= ‘0’;

when 2 => inic <= ‘1’; shift_r <= ‘0’; done <= ‘0’;

ce_c <= ‘0’; start_sq <= ‘0’; start_mult <= ‘0’;

when 3 => inic <= ‘0’; shift_r <= ‘0’; done <= ‘0’;

ce_c <= ‘1’; start_sq <= ‘1’; start_mult <= ee(0);

when 4 => inic <= ‘0’; shift_r <= ‘0’; done <= ‘0’;

ce_c <= ‘1’; start_sq <= ‘0’; start_mult <= ‘0’;

when 5 => inic <= ‘0’; shift_r <= ‘1’; done <= ‘0’;

ce_c <= ‘1’; start_sq <= ‘0’; start_mult <= ‘0’;

end case;

if reset = ‘1’ then current_state <= 0;

elsif clk’event and clk = ‘1’ then

case current_state is

when 0 => if start = ‘0’ then current_state <= 1;

end if;

when 1 => if start = ‘1’ then current_state <= 2;

end if;