Page 169 - Hardware Implementation of Finite-Field Arithmetic

P. 169

152 Cha pte r S i x

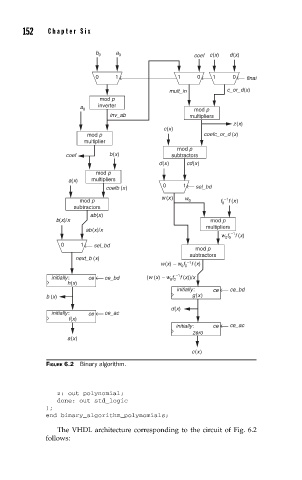

b 0 a 0 coef c(x) d(x)

0 1 1 0 1 0 final

mult_in c_or_d(x)

mod p

a 0 inverter mod p

inv_ab multipliers

z(x)

c(x)

mod p coefc_or_d (x)

multiplier

mod p

coef b(x) subtractors

d(x) cd(x)

mod p

a(x) multipliers

0 1 sel_bd

coefb (x)

w (x) w

mod p 0 f –1 f (x)

0

subtractors

ab(x)

b(x)/x mod p

multipliers

ab(x)/x

w f –1 f (x)

0 0

0 1 sel_bd

mod p

subtractors

next_b (x)

w(x) – w f –1 f (x)

0 0

initially: ce ce_bd (w (x) – w f –1 f (x))/x

0 0

h(x)

initially: ce ce_bd

b (x) g(x)

d(x)

initially: ce ce_ac

f(x)

initially: ce ce_ac

zero

a(x)

c(x)

FIGURE 6.2 Binary algorithm.

z: out polynomial;

done: out std_logic

);

end binary_algorithm_polynomials;

The VHDL architecture corresponding to the circuit of Fig. 6.2

follows: