Page 520 - Introduction to Information Optics

P. 520

9.4. Parallel Signed-Digit Arithmetic 505

Input b,

Stage 1 T,W T,W T,W T,W T,W

W 4 tj W 2 *2 W l t w

«5 i f o

l

1

Stage! rl \»1 T ,W I T1 )W1 T ,^ ri

1 1 .1 i j 1 ,

W 4 w, W, w t

Stage 3 T T T T

1 1 1 ! i • 1 1

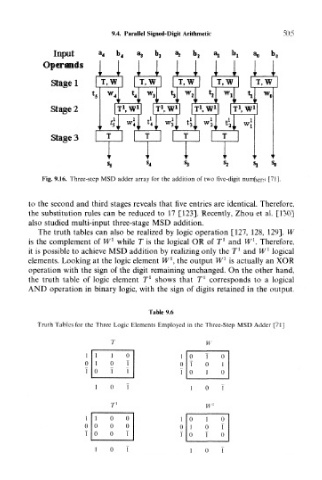

Fig. 9.16. Three-step MSD adder array for the addition of two five-digit numbers [71].

to the second and third stages reveals that five entries are identical. Therefore,

the substitution rules can be reduced to 17 [123]. Recently, Zhou et al. [130]

also studied multi-input three-stage MSD addition.

The truth tables can also be realized by logic operation [127, 128, 129]. W

1

1

1

is the complement of W while T is the logical OR of T and W . Therefore,

1

1

it is possible to achieve MSD addition by realizing only the T and W logical

1

elements. Looking at the logic element W , the output W^ is actually an XOR

operation with the sign of the digit remaining unchanged. On the other hand,

1

1

the truth table of logic element T shows that T corresponds to a logical

AND operation in binary logic, with the sign of digits retained in the output.

Table 9.6

Truth Tables for the Three Logic Elements Employed in the Three-Step MSD Adder [71]

T w

I I 1 0

0 1 0 1

1 0 1 1