Page 396 - Introduction to Microcontrollers Architecture, Programming, and Interfacing of The Motorola 68HC12

P. 396

12.6 The M-CORE Series 373

M-CORE edit instructions include ASR to shift a GPR right arithmetically a

number of bits specified by a GPR; ASRC to shift a GPR right arithmetically one bit,

putting the bit shifted out into C; ASRI to shift a GPR right arithmetically a number of

bits specified by an immediate operand; and similar instructions LSL,LSR,LSRC,

LSLI, LSLRI, and ROTLI. The last instruction is a circular shift of a GPR. The BREV

instruction reverses the bits in a GPR. XSR shifts a GPR one bit right, putting the bit

shifted out into the C bit. SEXTB sign extends a GPR from 8 to 32 bits, SEXTH sign

extends a GPR from 16 to 32 bits, ZEXTB zero extends a GPR from 8 to 32 bits, and

ZEXTH zero extends a GPR from 16 to 32 bits. XTRBO extracts byte zero (the LSbyte)

of any GPR to GPR register 1. XTRB1 similarly extracts byte one of any GPR, XTRB2

extracts byte two, and XTRB3 extracts byte three.

Addition and subtraction are unsigned, there being no V condition code bit needed for

a signed overflow check. But because data moved into a GPR can be sign-extended using

SEXTB or SEXTH, and addition and subtraction are 32-bit operations, a 32-bit signed

overflow is unlikely. Before a store instruction such as ST. B or ST. H, the high bits,

which are not stored, can be checked to see if they are all zeros or all ones.

The reader should observe that the M-CORE architecture has unusually extensive

logic and edit instructions. These instructions are valuable for I/O operations. However,

there are comparatively fewer arithmetic and move instructions in this RISC processor.

M -CORE control instructions include BR to branch to a relative address using an

11-bit relative address, BRT to branch if C is true, BRF to branch if C is false. JMP

copies a GPR into the PC, and JMP I jumps indirectly to an address at a word specified

by an 8-bit displacement. If the C bit is 1, the LOOPT instruction decrements a GPR

and branches backwards up to 15 instructions to implement a loop. Otherwise it

decrements the GPR and continues to execute the instruction below it.

JSR saves the PC in GPR register 15 and copies a GPR into the PC, and JSRI

saves the PC in GPR register 15 and jumps indirectly to an address at a word specified by

an 8-bit displacement. TRAP, having a 2-bit immediate operand, effects an exception

like an interrupt, through an address stored at 0x40 to Ox4f. TRAP and other exceptions

and interrupts save the processor status register (special purpose register 0) and return

address in status/control registers. The instruction RTE returns from an exception, and

RFI returns from a fast interrupt, restoring the saved PC and processor status register.

The instruction BKPT causes a breakpoint exception. It can be used to stop a

program so that the debugger can examine memory or registers and resume. WAIT

causes the processor to enter low-power wait mode in which all peripherals continue to

*

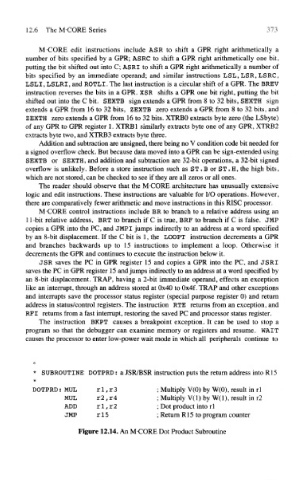

* SUBROUTINE DOTPRD: a JSR/BSR instruction puts the return address into R15

*

DOTPRD: MUL r 1, r3 ; Multiply V(0) by W(0), result in rl

MUL r 2, r 4 ; Multiply V( 1) by W( 1), result in r2

ADD rl, r2 ; Dot product into rl

JMP r!5 ; Return R15 to program counter

Figure 12.14. An M-CORE Dot Product Subroutine