Page 395 - Introduction to Microcontrollers Architecture, Programming, and Interfacing of The Motorola 68HC12

P. 395

372 Chapter 12 Other Microcontrollers

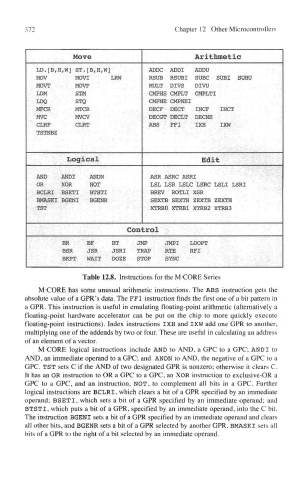

Table 12.8. Instructions for the M-CORE Series

M-CORE has some unusual arithmetic instructions. The ABS instruction gets the

absolute value of a GPR's data. The FF1 instruction finds the first one of a bit pattern in

a GPR. This instruction is useful in emulating floating-point arithmetic (alternatively a

floating-point hardware accelerator can be put on the chip to more quickly execute

floating-point instructions). Index instructions IXH and IXW add one GPR to another,

multiplying one of the addends by two or four. These are useful in calculating an address

of an element of a vector.

M-CORE logical instructions include AND to AND, a GPC to a GPC; AND I to

AND, an immediate operand to a GPC; and ANDN to AND, the negative of a GPC to a

GPC. TST sets C if the AND of two designated GPR is nonzero; otherwise it clears C.

It has an OR instruction to OR a GPC to a GPC, an XOR instruction to exclusive-OR a

GPC to a GPC, and an instruction, NOT, to complement all bits in a GPC. Further

logical instructions are BCLRI, which clears a bit of a GPR specified by an immediate

operand; BSETI, which sets a bit of a GPR specified by an immediate operand; and

BTSTI, which puts a bit of a GPR, specified by an immediate operand, into the C bit.

The instruction BGENI sets a bit of a GPR specified by an immediate operand and clears

all other bits, and BGENR sets a bit of a GPR selected by another GPR. BMASK1 sets all

bits of a GPR to the right of a bit selected by an immediate operand.