Page 217 - A Practical Guide from Design Planning to Manufacturing

P. 217

190 Chapter Six

Sum = ABC + ABC + ABC + ABC

Sum = A(B ⊕ C) + A(B ⊕ C)

Sum = A ⊕ B ⊕ C

Figure 6-17 Simplifying with XORs.

Unfortunately no real simplification was possible for the sum output.

Each of the four fundamental products has no neighbors, which means

that Karnaugh maps cannot help to reduce this function. A tactic that

helps in these cases is looking for XOR functions in the minimal sum.

In general, XORs tend to produce fundamental products with few or no

neighbors. Functions that cannot be reduced easily by Karnaugh maps

are often simplified using XORs. This process is shown for the sum func-

tion in Fig. 6-17.

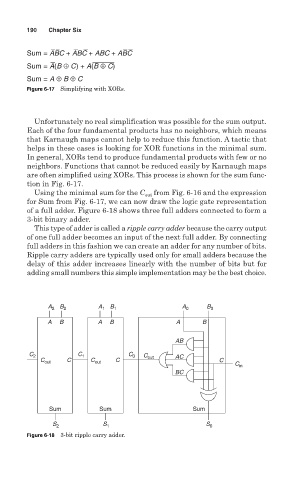

Using the minimal sum for the C out from Fig. 6-16 and the expression

for Sum from Fig. 6-17, we can now draw the logic gate representation

of a full adder. Figure 6-18 shows three full adders connected to form a

3-bit binary adder.

This type of adder is called a ripple carry adder because the carry output

of one full adder becomes an input of the next full adder. By connecting

full adders in this fashion we can create an adder for any number of bits.

Ripple carry adders are typically used only for small adders because the

delay of this adder increases linearly with the number of bits but for

adding small numbers this simple implementation may be the best choice.

A 2 B 2 A 1 B 1 A 0 B 0

A B A B A B

AB

C

C 2 1 C 0 C out AC

C out C C out C C C in

BC

Sum Sum Sum

S 2 S 1 S 0

Figure 6-18 3-bit ripple carry adder.