Page 177 - Phase-Locked Loops Design, Simulation, and Applications

P. 177

DESIGN PROCEDURE FOR MIXED-SIGNAL PLLS Ronald E. Best 109

The design procedure presented here is independent of the type of PLL circuit that will

finally be used to implement the system. The individual steps are described in the following.

As mentioned, most of the formulas used to design the PLL are listed in Tables 3.1 through

3.5. In the procedure explained in the following, the VCO is assumed to be a relaxation

oscillator VCO (as shown in Fig. 2.23). With some slight modifications, however, it can also

be applied to resonant-type VCOs. We add some comments at the end of this chapter

regarding the design of resonant VCOs that use varactor diodes to vary the output frequency.

Step 1. In the first step, the input and output frequencies of the PLL must be specified.

There are cases where both input frequency and output frequency are constant but not

necessarily identical. In other applications (for example, frequency synthesizers), the input

frequency is always the same, but the output frequency is variable. As a last variant, both input

and output frequencies could be variable. Let f and f be the minimum and maximum

1min 1max

input frequencies, and f 2min and f 2max the minimum and maximum output frequencies,

respectively.

Step 2. In this step, the scaler ratio must be determined. In some PLL applications, the

output frequency f always equals the reference frequency f . Here no down-scaler is

2

1

needed—in other words, N = 1. Cases exist where the ratio of output to reference frequency is

greater than 1 but remains fixed. Here, a down scaler with constant divider ratio N is required.

When the PLL is used to build a frequency synthesizer, the ratio of output to reference

frequency is variable; thus, a range for N must be defined (N ≤ N ≤ N ). When N is

min max

variable, natural frequency ω and damping factor ζ will vary with N, as seen from the

n

corresponding equations in Tables 3.1 through 3.5. Both of these parameters will vary

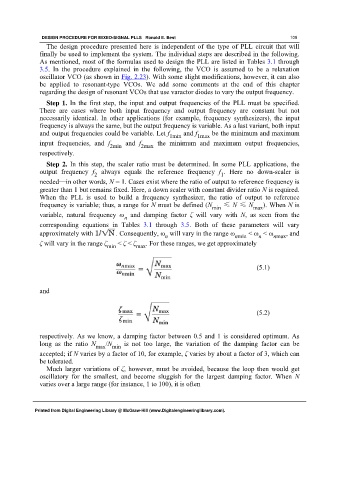

approximately with . Consequently, ω will vary in the range ω < ω < ω , and

n nmin n nmax

ζ will vary in the range ζ < ζ < ζ . For these ranges, we get approximately

min max

(5.1)

and

(5.2)

respectively. As we know, a damping factor between 0.5 and 1 is considered optimum. As

long as the ratio N max /N min is not too large, the variation of the damping factor can be

accepted; if N varies by a factor of 10, for example, ζ varies by about a factor of 3, which can

be tolerated.

Much larger variations of ζ, however, must be avoided, because the loop then would get

oscillatory for the smallest, and become sluggish for the largest damping factor. When N

varies over a large range (for instance, 1 to 100), it is often

Printed from Digital Engineering Library @ McGraw-Hill (www.Digitalengineeringlibrary.com).