Page 197 - Programming Microcontrollers in C

P. 197

182 Chapter 4 Small 8-Bit Systems

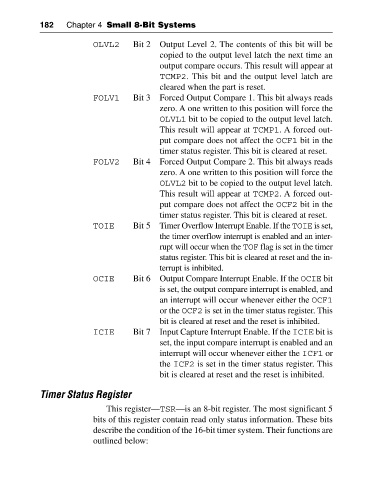

OLVL2 Bit 2 Output Level 2. The contents of this bit will be

copied to the output level latch the next time an

output compare occurs. This result will appear at

TCMP2. This bit and the output level latch are

cleared when the part is reset.

FOLV1 Bit 3 Forced Output Compare 1. This bit always reads

zero. A one written to this position will force the

OLVL1 bit to be copied to the output level latch.

This result will appear at TCMP1. A forced out

put compare does not affect the OCF1 bit in the

timer status register. This bit is cleared at reset.

FOLV2 Bit 4 Forced Output Compare 2. This bit always reads

zero. A one written to this position will force the

OLVL2 bit to be copied to the output level latch.

This result will appear at TCMP2. A forced out

put compare does not affect the OCF2 bit in the

timer status register. This bit is cleared at reset.

TOIE Bit 5 Timer Overflow Interrupt Enable. If the TOIE is set,

the timer overflow interrupt is enabled and an inter

rupt will occur when the TOF flag is set in the timer

status register. This bit is cleared at reset and the in

terrupt is inhibited.

OCIE Bit 6 Output Compare Interrupt Enable. If the OCIE bit

is set, the output compare interrupt is enabled, and

an interrupt will occur whenever either the OCF1

or the OCF2 is set in the timer status register. This

bit is cleared at reset and the reset is inhibited.

ICIE Bit 7 Input Capture Interrupt Enable. If the ICIE bit is

set, the input compare interrupt is enabled and an

interrupt will occur whenever either the ICF1 or

the ICF2 is set in the timer status register. This

bit is cleared at reset and the reset is inhibited.

Timer Status Register

This register—TSR—is an 8-bit register. The most significant 5

bits of this register contain read only status information. These bits

describe the condition of the 16-bit timer system. Their functions are

outlined below: