Page 356 - ARM 64 Bit Assembly Language

P. 356

346 Chapter 10

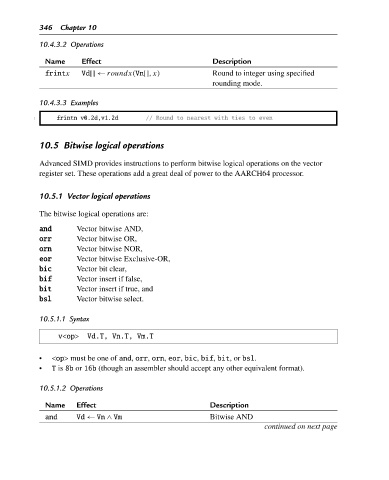

10.4.3.2 Operations

Name Effect Description

frintx Vd[] ← roundx(Vn[],x) Round to integer using specified

rounding mode.

10.4.3.3 Examples

1 frintn v0.2d,v1.2d // Round to nearest with ties to even

10.5 Bitwise logical operations

Advanced SIMD provides instructions to perform bitwise logical operations on the vector

register set. These operations add a great deal of power to the AARCH64 processor.

10.5.1 Vector logical operations

The bitwise logical operations are:

and Vector bitwise AND,

orr Vector bitwise OR,

orn Vector bitwise NOR,

eor Vector bitwise Exclusive-OR,

bic Vector bit clear,

bif Vector insert if false,

bit Vector insert if true, and

bsl Vector bitwise select.

10.5.1.1 Syntax

v<op> Vd.T, Vn.T, Vm.T

• <op> must be one of and, orr, orn, eor, bic, bif, bit,or bsl.

• T is 8b or 16b (though an assembler should accept any other equivalent format).

10.5.1.2 Operations

Name Effect Description

and Vd ← Vn ∧ Vm Bitwise AND

continued on next page