Page 360 - ARM 64 Bit Assembly Language

P. 360

350 Chapter 10

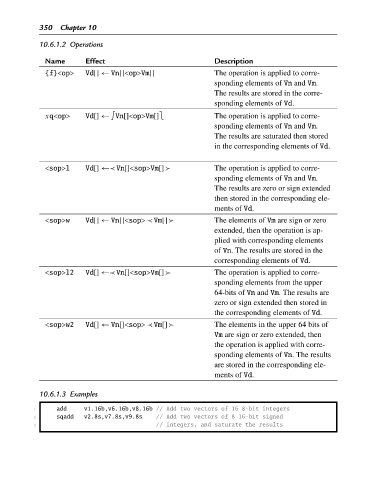

10.6.1.2 Operations

Name Effect Description

{f}<op> Vd[] ← Vn[]<op>Vm[] The operation is applied to corre-

sponding elements of Vn and Vm.

The results are stored in the corre-

sponding elements of Vd.

xq<op> Vd[] ← Vn[]<op>Vm[] The operation is applied to corre-

sponding elements of Vn and Vm.

The results are saturated then stored

in the corresponding elements of Vd.

<sop>l Vd[] ←≺Vn[]<sop>Vm[] The operation is applied to corre-

sponding elements of Vn and Vm.

The results are zero or sign extended

then stored in the corresponding ele-

ments of Vd.

<sop>w Vd[] ← Vn[]<sop> ≺Vm[] The elements of Vm are sign or zero

extended, then the operation is ap-

plied with corresponding elements

of Vn. The results are stored in the

corresponding elements of Vd.

<sop>l2 Vd[] ←≺Vn[]<sop>Vm[] The operation is applied to corre-

sponding elements from the upper

64-bits of Vn and Vm. The results are

zeroorsignextendedthenstoredin

the corresponding elements of Vd.

<sop>w2 Vd[] ← Vn[]<sop> ≺Vm[] The elements in the upper 64 bits of

Vm are sign or zero extended, then

the operation is applied with corre-

sponding elements of Vn. The results

are stored in the corresponding ele-

ments of Vd.

10.6.1.3 Examples

1 add v1.16b,v6.16b,v8.16b // Add two vectors of 16 8-bit integers

2 sqadd v2.8s,v7.8s,v9.8s // Add two vectors of 8 16-bit signed

3 // integers, and saturate the results