Page 357 - ARM 64 Bit Assembly Language

P. 357

Advanced SIMD instructions 347

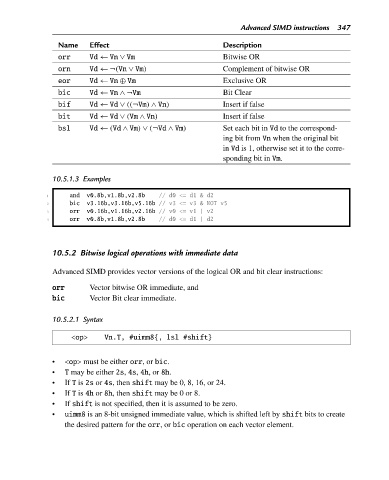

Name Effect Description

orr Vd ← Vn ∨ Vm Bitwise OR

orn Vd ←¬(Vn ∨ Vm) Complement of bitwise OR

eor Vd ← Vn ⊕ Vm Exclusive OR

bic Vd ← Vn ∧¬Vm Bit Clear

bif Vd ← Vd ∨ ((¬Vm) ∧ Vn) Insert if false

bit Vd ← Vd ∨ (Vm ∧ Vn) Insert if false

bsl Vd ← (Vd ∧ Vm) ∨ (¬Vd ∧ Vm) Set each bit in Vd to the correspond-

ing bit from Vn when the original bit

in Vd is 1, otherwise set it to the corre-

sponding bit in Vm.

10.5.1.3 Examples

1 and v0.8b,v1.8b,v2.8b // d0 <= d1 & d2

2 bic v3.16b,v3.16b,v5.16b // v3 <= v3 & NOT v5

3 orr v0.16b,v1.16b,v2.16b // v0 <= v1 | v2

4 orr v0.8b,v1.8b,v2.8b // d0 <= d1 | d2

10.5.2 Bitwise logical operations with immediate data

Advanced SIMD provides vector versions of the logical OR and bit clear instructions:

orr Vector bitwise OR immediate, and

bic Vector Bit clear immediate.

10.5.2.1 Syntax

<op> Vn.T, #uimm8{, lsl #shift}

• <op> must be either orr,or bic.

• T may be either 2s, 4s, 4h,or 8h.

• If T is 2s or 4s,then shift may be 0, 8, 16, or 24.

• If T is 4h or 8h,then shift may be 0 or 8.

• If shift is not specified, then it is assumed to be zero.

• uimm8 is an 8-bit unsigned immediate value, which is shifted left by shift bits to create

the desired pattern for the orr,or bic operation on each vector element.